Static Timing Analysis for Nanometer Designs:A Practical Approach(v2)

绪论

众所周知,静态时序分析是IC工程师必备知识点,也是秋招中笔试面试的高频考点。

网上不乏优秀视频课,如V3学院尤老师、小梅哥、IC创新学院邸志雄老师的课。

《Static Timing Analysis for Nanometer Designs:A Practical Approach》,可堪称静态时序分析的“圣经”吧!

由于网上找不到此书的翻译,因此笔者决定开坑进行对“圣经”的翻译~!希望可以在加深对静态时序分析的学习同时,完成这一本书的翻译方便大家以后更好地从中学习吧。

本章节概述了纳米级(nanometer)设计下的静态时序仿真过程

本章节解决了如下问题:

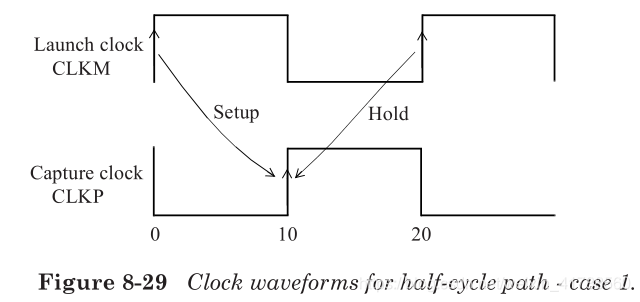

- 什么是静态时序分析(static timing analysis)?

- 噪声(noise)与串扰(crosstalk)会带来什么影响 ?

- 如何使用静态时序分析?

- 在整个设计流程中的哪个阶段会应用静态时序分析?

纳米设计

在半导体器件中,金属互连走线通常用于在电路的各个部分之间建立连接以实现设计。众所周知,随着工艺技术的缩小,这些互连走线会影响设计的性能。对于深亚微米或纳米工艺技术,互连中的耦合会引起噪声和串扰——这两种情况都会限制设计的运行速度。虽然噪声和耦合效应在老一代技术中可以忽略不计,但它们在纳米技术中发挥着重要作用。因此,物理设计应考虑串扰和噪声的影响,然后设计验证应包括串扰和噪声的影响。

什么是静态时序分析?

静态时序分析(也称为 STA)是可用于验证数字设计时序的众多技术之一。用于验证时序的另一种方法是时序仿真,它可以验证设计的功能和时序。术语时序分析用于指代这两种方法之一 - 静态时序分析或时序仿真。因此,时序分析只是指对时序问题的设计进行分析。

STA 是静态的,因为设计分析是静态执行的,不依赖于施加到输入引脚的数据值。这与基于仿真的时序分析形成对比,在基于仿真的时序分析中,对输入信号应用刺激,观察并验证结果行为,然后随着新输入刺激的应用而推进时间,并观察和验证新行为,依此类推。

给定一个设计以及一组输入时钟定义和设计外部环境的定义,静态时序分析的目的是验证设计是否可以以额定速度运行。也就是说,设计可以在指定的时钟频率下安全运行,而不会出现任何时序违规。图 1-1 展示了静态时序分析的基本功能 。DUA 是被分析的设计。一些时序检查的例子是建立和保持检查。建立检查确保数据可以在给定的时钟周期内到达触发器。保持检查确保数据至少保持最短时间,从而不会出现意外的数据通过触发器:也就是说,它确保触发器正确捕获预期数据。这些检查确保正确的数据已准备就绪并可用于捕获并锁定新状态。

静态时序分析更重要的方面是对整个设计进行一次分析,并对设计的所有可能路径和场景执行所需的时序检查。因此,STA 是一种用于验证设计时序的完整而详尽的方法。

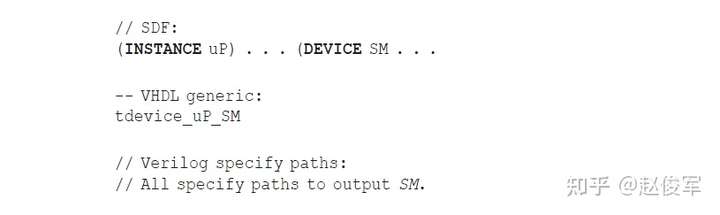

分析中的设计通常使用指定的硬件描述语言(例如 VHDL 或 Verilog HDL)。外部环境(包括时钟定义)通常使用 SDC或等效格式指定。 SDC 是一种时序约束规范语言。时序报告采用 ASCII 格式,通常有多列,每一列显示路径延迟的一个属性。

为什么使用静态时序分析?

静态时序分析是对设计的所有时序检查的完整而详尽的验证。其他时序分析方法(例如仿真)只能验证设计中受激励影响的部分。通过时序仿真进行验证与所使用的测试向量一样详尽。模拟和验证具有 10-1亿个门的设计的所有时序条件非常缓慢,并且无法完全验证时序。因此,很难通过模拟进行详尽的验证。

另一方面,静态时序分析提供了一种更快、更简单的方法来检查和分析设计中的所有时序路径是否存在任何时序违规。考虑到当今 ASIC 的复杂性,其中可能包含 10 到 1 亿个门,静态时序分析已成为详尽验证设计时序的必要条件。

串扰和噪声(Crosstalk and Noise)

设计功能及其性能可能会受到噪声的限制。噪声是由于与其他信号的串扰或主输入或电源上的噪声而产生的。噪声影响可以限制设计运作频率,并且也可能导致功能故障。因此,一个设计实现必须经过验证证明它的稳健性,这意味着它可以在不影响设计的额定性能情况下承受噪声。

基于逻辑仿真的验证无法处理串扰、噪声和片上变化的影响。

本书中描述的分析方法不仅涵盖了传统的时序分析技术,还涵盖了噪声分析,以验证包括噪声影响在内的设计。

设计流程

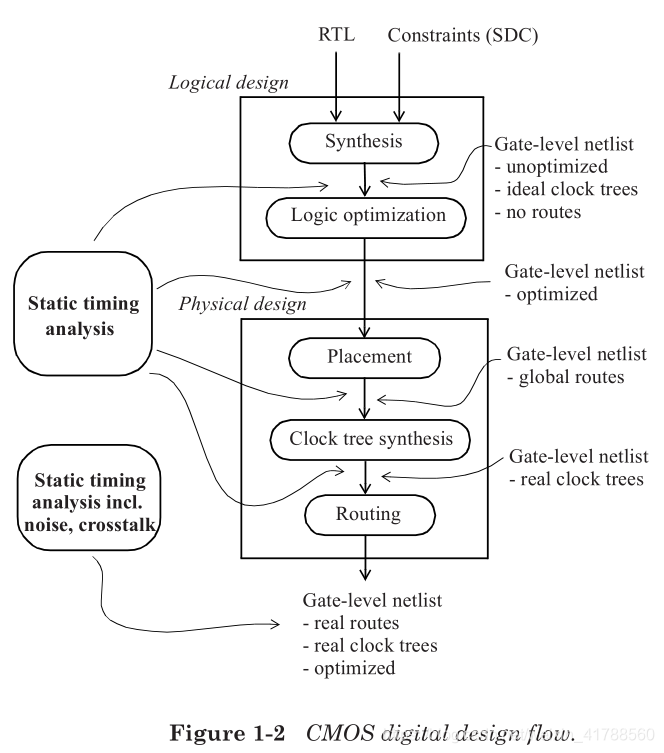

本节主要描述本书其余部分使用的上下文中的 CMOS数字设计流程。还简要描述了它对 FPGA 和异步设计的适用性。

CMOS数字设计

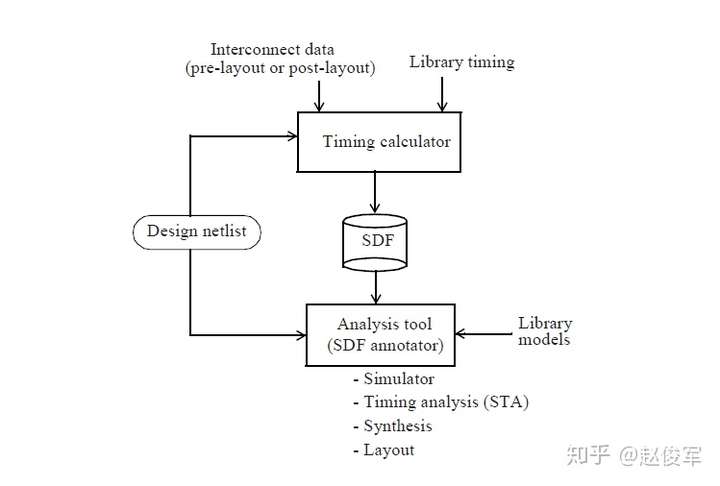

在 CMOS 数字设计流程中,静态时序分析可以在实现的许多不同阶段执行。图 1-2 显示了一个典型的流程。

STA 很少在 RTL 级别完成,因为此时验证设计的功能性比验证时序更为重要。也不是所有的时序信息都可用,因为块的描述在行为级。一旦 RTL 级的设计被综合到门级,STA 用于验证设计的时序。STA 也可以在执行逻辑优化之前运行 - 目标是识别最差或关键的时序路径。 STA可以在逻辑优化后重新运行来查看是否仍有需要优化的失败路径,或确定关键路径。

在物理设计开始时,时钟树被认为是理想的,即它们具有零延迟。一旦物理设计开始并且在时钟树构建之后,就可以执行 STA 来再次检查时序。实际上,在物理设计期间,可以在每一步执行 STA 以识别最差路径。

在物理实现中,逻辑单元通过互连金属走线连接。金属走线的寄生 RC(电阻和电容)会影响通过这些走线的信号路径延迟。在典型的纳米设计中,互连的寄生效应可以解释设计中的大部分延迟和功耗。因此,任何设计分析都应评估互连对性能特征(速度、功率等)的影响。如前所述,信号走线之间的耦合会产生噪声,设计验证必须包括噪声对性能的影响。

在逻辑设计阶段,由于没有与布局相关的物理信息,因此可以假设为理想互连;可能更有兴趣查看导致最坏路径的逻辑。此阶段使用的另一种技术是使用线载模型估算互连的长度。线载模型根据单元的扇出提供估计的 RC。

在最终确定走线的布线( routing)之前,实施工具使用布线距离的估计来获得布线的 RC 寄生效应。由于布线还没有最终确定,所以这个阶段称为全局布线阶段(global route),以区别于最终布线阶段(final route)。在物理设计的全局布线阶段,简化布线用于估计布线长度,布线估计用于确定计算布线延迟所需的电阻和电容。在这个阶段,不能包括耦合的影响。详细布线完成后,使用提取工具得到的实际 RC 值,可以分析耦合的影响。但是,物理设计工具可能仍会使用近似值来帮助改善计算 RC 值的运行时间。

提取工具用于从布线设计中提取详细的寄生参数(RC 值)。这样的提取工具可以选择在迭代优化期间以较小的运行时间和较不精确的RC值获得寄生参数,也可以选择在最终验证过程中以较大的运行时间提取非常精确的RC值。

总而言之,静态时序分析可以在门级网表上执行,具体取决于:

- 互连(interconnect)是怎么建模 的-——理想互连、线载模型、具有近似 RC 的全局布线或具有准确 RC 的真实布线。

- 时钟是怎么建模 的-——时钟是理想的(零延迟)还是传播的(实际延迟)。

- 是否包括信号之间的耦合——是否分析了任何串扰噪声。

图 1-2 似乎暗示 STA 是在实现步骤之外完成的,也就是说,STA 是在每个综合、逻辑优化和物理设计步骤之后完成的。实际上,这些步骤中的每一个都在其功能范围内执行集成(和增量)STA。例如,逻辑优化步骤中的时序分析引擎,它是用于识别优化器需要处理的关键路径。同样,布局工具中的集成时序分析引擎用于在布局逐步进行时保持设计的时序。

FPGA设计

STA 的基本流程在 FPGA 中仍然有效。尽管 FPGA 中的布线受限于通道,但提取寄生效应和执行 STA 的机制与 CMOS 数字设计流程相同。例如,STA执行时,可以假设互联是理想的,或者使用线载模型,假设时钟树是理想的或真实的,假设全局布线,或者使用真实布线进行寄生。

异步设计

STA 的原理也适用于异步设计。人们可能对从设计中的一个信号到另一个信号的时序更感兴趣,而不是对可能不存在的情况进行建立和保持检查。因此,大多数检查可能是点对点时序检查,或偏斜 STA 检查。用于分析耦合引起的毛刺的噪声分析适用于任何设计——异步或同步。此外,噪声分析对时序的影响,包括耦合的影响,也适用于异步设计。

不同设计阶段的STA

在逻辑级(门级,还没有物理设计),STA可以使用:

- 理想互连或基于线载模型的互连。

- 具有延迟和抖动估计值的理想时钟。

在物理设计阶段,除了上述模式外,STA 还可以使用:

- 互连 -——范围可以从全局布线估计、具有近似提取的真实布线或具有准确signoff提取的真实路由。

- 时钟树 -——真正的时钟树。

- 包括和不包括串扰的影响

静态时序分析的局限性

虽然时序和噪声分析在分析所有可能情况下的时序问题方面做得非常出色,但最先进的技术仍然不允许 STA 完全取代仿真。 这是因为在时序验证的一些方面不能被STA 完全捕获和验证。

STA的一些局限性:

- 复位顺序:检查在异步或同步复位后,所有触发器是否复位到其所需的逻辑值。这是无法使用静态计时分析进行检查的。芯片可能无法复位。这是因为某些声明(如信号的初始值)不会被合成,只能在模拟过程中进行验证。

- X处理:STA技术只处理逻辑0和逻辑1(或者高和低)、上升和下降的逻辑域。设计中的未知值X会导致不确定值在设计中传播,这无法通过STA进行检查。尽管STA中的噪声分析可以通过设计分析和传播 glitches,但 glitches分析和传播的范围与作为基于模拟的纳米设计时序验证一部分的X处理非常不同。

- PLL设置:PLL配置可能未正确加载或设置。

- 异步时钟域交叉:STA不检查是否使用了正确的时钟同步器。需要其他工具来确保在存在异步时钟域交叉的地方存在正确的时钟同步器。

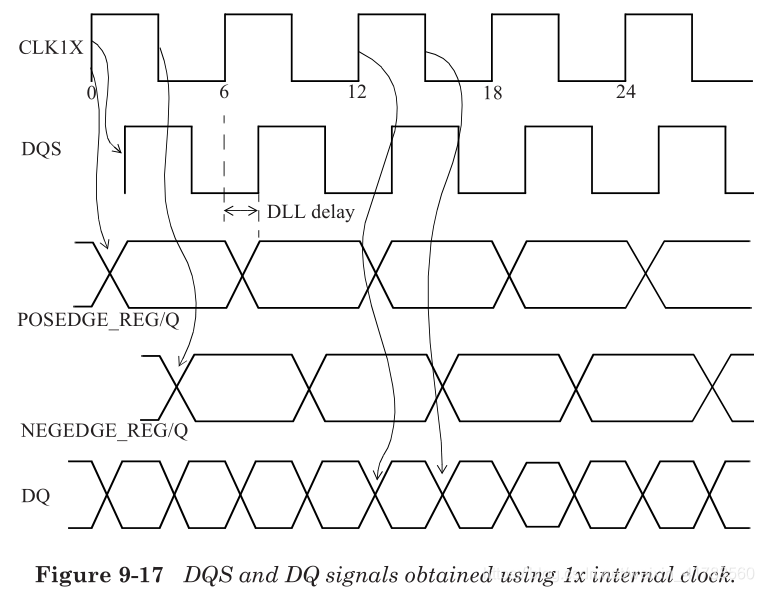

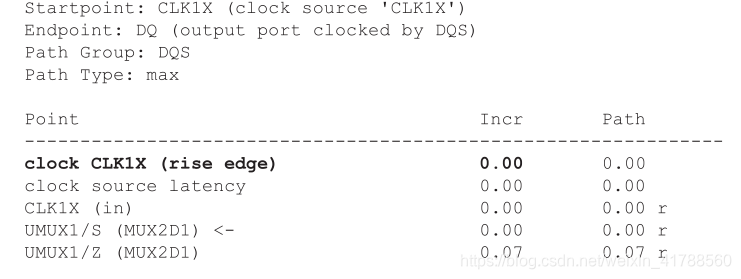

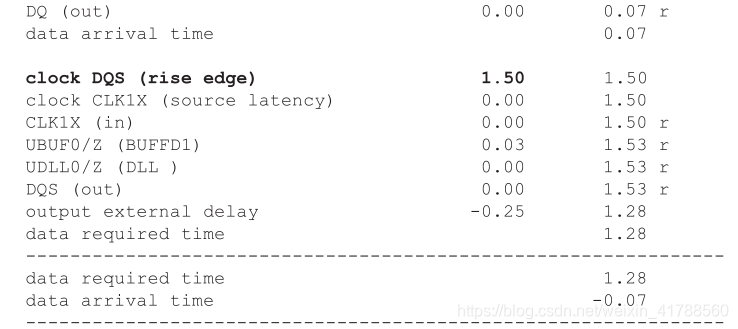

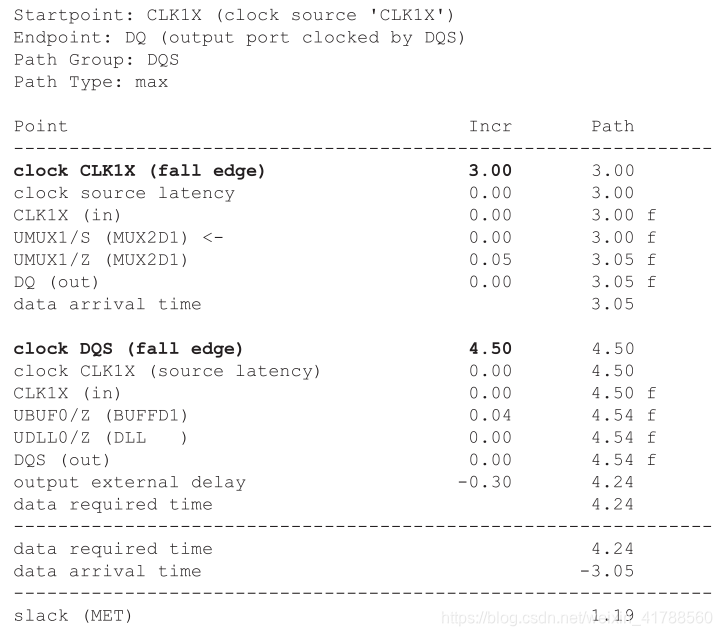

- IO接口时序:可能无法仅根据STA约束指定IO接口要求。例如,设计者可以使用SDRAM仿真模型为双数据速率(Double Data Rate,DDR)接口选择详细的电路级仿真。模拟的目的是确保可以以足够的余量读取和写入存储器,而且,如果有延迟锁相环(Delay Locked Loop,DLL),可以控制DLL以便在必要时对齐信号。

- 模拟和数字块之间的接口:由于STA不处理模拟块,验证方法需要确保这两种块之间的连接正确。

- 错误路径(False paths):静态时序分析验证通过逻辑路径的时序是否满足所有约束,如果通过逻辑路径的时序不符合要求的规范,则标记违规。在许多情况下,STA 可能会将逻辑路径标记为失败路径,即使逻辑可能永远无法通过该路径传播。当系统应用程序从不使用这样的路径或者在故障路径的敏感化期间使用相互矛盾的条件时,就会发生这种情况。这种时序路径被称为虚假路径,因为它们永远无法实现。在设计中指定适当的时序约束(包括错误路径和多周期路径约束)时,STA 结果的质量会更好。在大多数情况下,设计人员可以利用设计的固有知识并指定约束条件,以便在 STA 期间消除错误路径。

- FIFO 指针不同步:当两个期望同步的有限状态机实际上不同步时,STA 无法检测到问题。在功能仿真期间,两个有限状态机可能始终同步并同步变化。然而,在考虑延迟之后,有限状态机中的一个可能与另一个不同步,很可能是因为一个有限状态机比另一个更早退出复位。这种情况是STA无法检测到的。

- 时钟同步逻辑:STA无法检测时钟生成逻辑与时钟定义不匹配的问题。 STA 假设时钟发生器将提供时钟定义中指定的波形。可能对时钟发生器逻辑执行了错误的优化,例如导致在其中一条可能没有受到适当的约束路径上插入大延迟。或者,添加的逻辑可能会改变时钟的占空比。 STA 无法检测到这些潜在条件中的任何一个。

- 跨时钟周期的功能行为:静态时序分析无法建模或模拟跨时钟周期变化的功能行为。

尽管存在这些问题,STA 被广泛用于验证设计的时序,并且带有时序或带有单位延迟的仿真用于检查极端情况的备份,更简单地用于验证设计的正常功能模式。

功率考虑

功耗是设计实施中的一个重要考虑因素。大多数设计需要在电路板和系统的功率预算内运行。由于符合标准和/或由于芯片必须在其中运行的电路板或系统上的热预算,也可能引起功率考虑。总功率和待机功率通常有单独的限制。待机功率限制通常适用于手持设备或电池供电设备。

在大多数实际设计中,功率和时序通常是齐头并进的。设计人员希望使用更快(或更高速度)的单元来满足速度考虑,但可能会遇到可用功耗的限制。在为设计选择工艺技术和单元库时,功耗是一个重要的考虑因素。

可靠性考虑

设计实现必须满足可靠性要求。如第 1.4.1 节所述,金属互连走线具有限制设计性能的寄生 RC。除了寄生效应之外,还需要设计金属走线宽度,同时考虑可靠性因素。例如,高速时钟信号需要足够宽才能满足可靠性考虑,例如电迁移。

书的大纲

虽然静态时序分析从表面上看可能是一个非常简单的概念,但这种分析背后有很多背景知识。基本概念范围从单元延迟的准确表示到以最小的悲观计算最坏的路径延迟。计算单元延迟、组合块计时、时钟关系、多个时钟域和门控时钟的概念构成了静态时序分析的重要基础。为设计编写正确的 SDC 确实是一个挑战。

这本书是按照自下而上的顺序编写的——首先介绍简单的概念,然后在后面的章节中介绍更高级的主题。本书首先介绍了准确的单元延迟(第 3 章)。以有效的方式估计或计算精确的互连延迟及其表示是第 4 章的主题。计算由单元和互连组成的路径的延迟是第 5 章的主题。信号完整性,即信号切换对相邻网络的影响以及它如何影响沿路径的延迟,是第 6 章的主题。准确地表示具有时钟定义和路径异常的 DUA 环境是第 7 章的主题。STA 中执行的时序检查的详细信息在第 6 章中描述8. 跨各种接口的 IO 时序建模是第 9 章的主题。最后,第 10 章详细介绍高级时序检查,例如片上变化、时钟门控检查、电源管理和统计时序分析。附录提供了 SDC(用于表示时序约束)、SDF(用于表示单元和网络的延迟)和 SPEF(用于表示寄生)的详细描述。

第 7 章到第 10 章提供了 STA 验证的核心。前面的章节为更好地理解STA所需的nuts

and bolts 知识提供了坚实的基础和详细描述。

STA概念

介绍 CMOS 逻辑的基础知识以及与静态时序分析相关的时序术语。

CMOS 逻辑设计

MOS基本结构

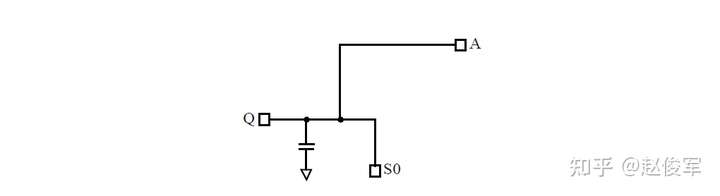

图2.1描述了MOS晶体管(NMOS和PMOS)的物理实现。源区和漏区之间的距离是MOS晶体管的沟道长度。用于构建 MOS 晶体管的最小沟道长度通常是 CMOS 技术工艺的最小特征尺寸。例如,0.25mm 技术允许制造沟道长度为 0.25mm 或更大的 MOS 晶体管。通过缩小通道几何形状,晶体管尺寸变得更小,随后在给定区域中可以封装更多晶体管。正如我们将在本章后面看到的,这也允许设计以更快的速度运行。

CMOS 逻辑门

CMOS 逻辑门是使用 NMOS 和 PMOS 晶体管构建的。图 2-2 显示了 CMOS 反相器的示例。根据输入的状态,CMOS 反相器有两种稳定状态。当输入 A 为低电平(Vss 或逻辑 0)时,NMOS 晶体管关闭,PMOS 晶体管开启,导致输出 Z 被拉至 Vdd,即逻辑 1。当输入 A 为高电平(Vdd 或逻辑 1)时,NMOS 晶体管导通,PMOS 晶体管关闭,导致输出 Z 被拉至 Vss,即逻辑 0。在上述两种状态中的任何一种状态下,CMOS 反相器都是稳定的,并且不会从输入 A 或电源 Vdd 汲取任何电流。

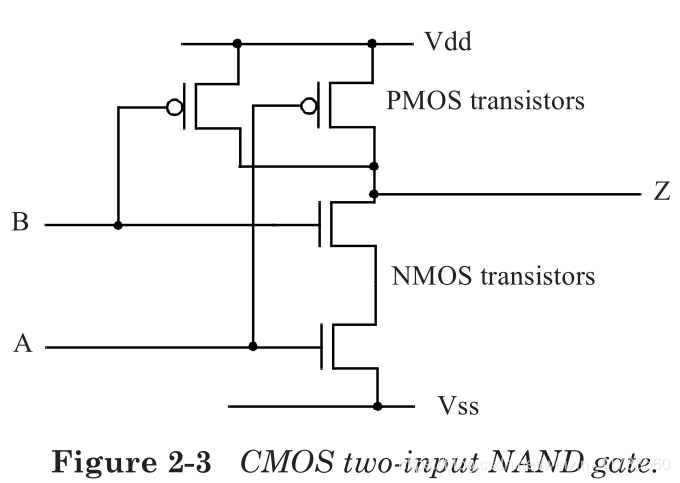

CMOS 反相器的特性可以扩展到任何 CMOS 逻辑门。在 CMOS 逻辑门中,输出节点通过上拉结构(由 PMOS 晶体管组成)连接到 Vdd,通过下拉结构(由 NMOS 晶体管组成)连接到 Vss。例如,图 2-3 显示了一个两输入 CMOS 与非门。在本例中,上拉结构由两个并联的 PMOS 晶体管组成,下拉结构由两个串联的 NMOS 晶体管组成。

对于任何 CMOS 逻辑门,上拉和下拉结构都是互补的。对于逻辑 0 或逻辑 1 的输入,这意味着如果上拉级打开,下拉级将关闭,同样如果上拉级关闭,下拉级将被关闭在。下拉和上拉结构由 CMOS 门实现的逻辑功能控制。例如,在CMOS与非门中,控制下拉结构的功能是“A和B”,即在A和B都为逻辑1时开启下拉。同理,控制上拉结构的函数是“not A or not B”,即在A或B逻辑-0时开启上拉。这些特性确保基于控制上拉结构的功能将输出节点逻辑拉至 Vdd。由于下拉结构是由一个互补功能控制。

对于逻辑 0 或逻辑 1 的输入,CMOS 逻辑门在稳定状态下不会从输入或电源汲取任何电流,因为上拉和下拉结构不能同时打开 1。 CMOS 逻辑的另一个重要方面是输入仅对前一级构成容性负载。

CMOS逻辑门是一个反相门,意思是单个开关输入(上升或下降)只能引起输出反方向开关,即输出不能与开关输入同方向开关。然而,CMOS 逻辑门可以级联以组合更复杂的逻辑功能 - 反相和非反相。

标准单元

芯片中的大多数复杂功能通常使用基本构建块设计,这些构建块实现简单的逻辑功能,例如和、或、与非、与或反转、或与反转和触发器。这些基本构建块是预先设计的,被称为标准单元(standard cells)。标准单元的功能和时序是预先表征的,可供设计人员使用。然后,设计人员可以使用标准单元作为构建块来实现所需的功能。

前一小节中描述的 CMOS 逻辑门的关键特性适用于所有 CMOS 数字设计。所有数字 CMOS 单元都设计为在输入处于稳定逻辑状态时没有从电源汲取电流(泄漏除外)。因此,大部分功耗与设计中的活动有关,并且是由设计中 CMOS 单元输入的充电和放电引起的。

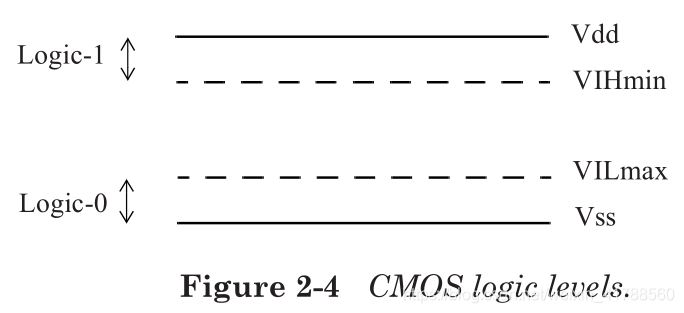

什么是逻辑 1 或逻辑 0?在 CMOS 单元中,两个值 VIHmin 和 VILmax 定义了限值。也就是说,任何高于 VIHmin 的电压值都被视为逻辑 1,而任何低于 VILmax 的电压值都被视为逻辑 0。参见图 2-4。具有 1.2V Vdd 电源的 CMOS 0.13mm 反相器单元的典型值为 VILmax 的 0.465V 和 VIHmin 的 0.625V。 VIHmin 和 VILmax 值源自电池的直流传输特性。直流传输特性在第 6.2.3 节中有更详细的描述。

有关 CMOS 技术的更多详细信息,请参阅参考书目中列出的相关文本之一。

CMOS 单元的建模

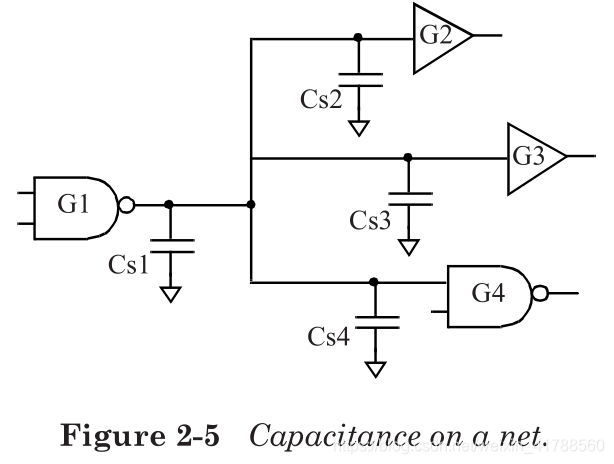

如果一个单元输出引脚驱动多个扇出单元,则单元输出引脚上的总电容是它所驱动的单元的所有输入电容之和加上构成网络的所有线段的电容之和加上驱动单元的输出电容。请注意,在 CMOS 单元中,单元的输入仅呈现电容性负载。

图 2-5 显示了一个单元格 G1 驱动其他三个单元格 G2、G3 和 G4 的示例。 Cs1、Cs2、Cs3 和 Cs4 是构成网络的线段的电容值。因此:

1 | Total cap (Output G1) = Cout(G1) + Cin(G2) + Cin(G3) + |

这是当单元 G1 切换时需要充电或放电的电容,因此该总电容值会影响单元 G1 的时序。

从时序的角度来看,我们需要对 CMOS 单元进行建模,以帮助我们分析通过单元的时序。对于每个输入引脚指定输入引脚电容。虽然大多数 CMOS 逻辑单元不包括输出引脚的引脚电容,但也可能存在输出引脚电容。

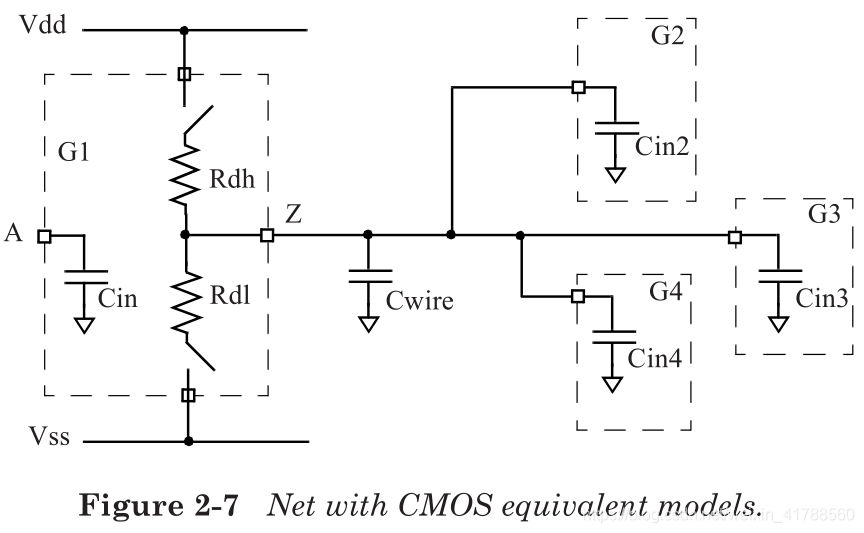

当输出为逻辑 1 时,输出级的上拉结构开启,并提供从输出到 Vdd 的路径。类似地,当输出为逻辑 0 时,输出级的下拉结构提供了从输出到 Vss 的路径。当 CMOS 单元切换状态时,切换速度取决于输出网络上的电容充电或放电的速度。输出网络上的电容(图 2-5)分别通过上拉和下拉结构充电和放电。请注意,上拉和下拉结构中的通道对输出充电和放电路径构成电阻。充电和放电路径电阻是决定 CMOS 单元速度的主要因素。上拉电阻的倒数称为电池的输出高驱动。输出上拉结构越大,上拉电阻越小,单元的输出高驱动越大。更大的输出结构也意味着单元的面积更大。输出上拉结构越小,单元面积越小,其输出高驱动也越小。上拉结构的相同概念可以应用于决定下拉路径电阻和输出低电平驱动的下拉结构。通常,单元被设计为具有相似的驱动强度(大或小)用于上拉和下拉结构。

输出驱动决定了可以驱动的最大容性负载。最大容性负载决定了扇出的最大数量,即它可以驱动多少个其他单元。较高的输出驱动对应于较低的输出上拉和下拉电阻,这允许电池在输出引脚上对较高的负载进行充电和放电。

图 2-6 显示了 CMOS 单元的等效抽象模型。该模型的目标是抽象单元的时序行为,因此仅对输入和输出阶段进行建模。该模型不捕获单元固有延迟或电气行为。

CpinA 是输入 A 上单元的输入引脚电容。 Rdh 和 Rdl 是单元的输出驱动电阻,并根据单元驱动的负载确定输出引脚 Z 的上升和下降时间。该驱动器还决定了单元的最大扇出限制。

图 2-7 显示了与图 2-5 相同的网络,但具有等效的单元模型。

1 | Cwire = Cs1 + Cs2 + Cs3 + Cs4 |

在上面的表达式中,Rout 是 Rdh 或 Rdl 之一,其中 Rdh 是上拉的输出驱动电阻,Rdl 是下拉的输出驱动电阻。

开关波形

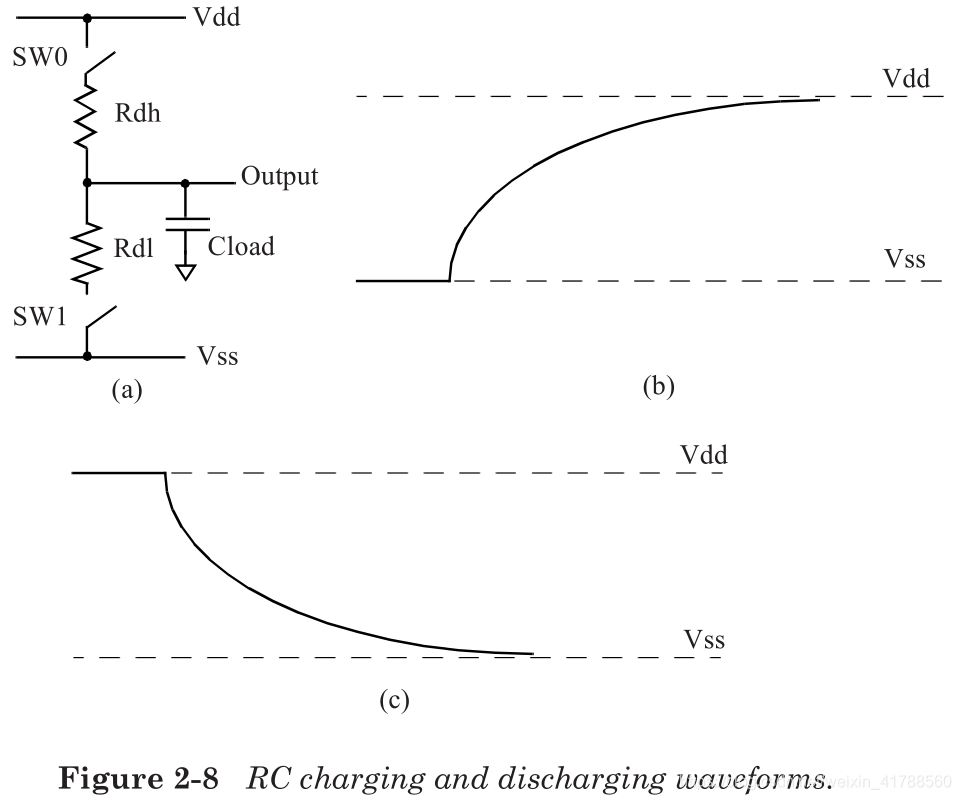

当通过激活 SW0 开关将电压施加到 RC 网络时,如图 2-8(a) 所示,输出变为逻辑 1。假设 SW0 激活时输出为 0V,输出端的电压转换由以下等式描述:

这种上升的电压波形如图 2-8(b) 所示。乘积 (Rdh * Cload) 称为 RC 时间常数 - 通常这也与输出的转换时间有关。

当输出从逻辑 1 变为逻辑 0 时,由于输入变化导致 SW0 断开连接并激活 SW1,输出转换如图 2-8(c) 所示。输出电容通过打开的 SW1 开关放电。这种情况下的电压转换由以下等式描述:

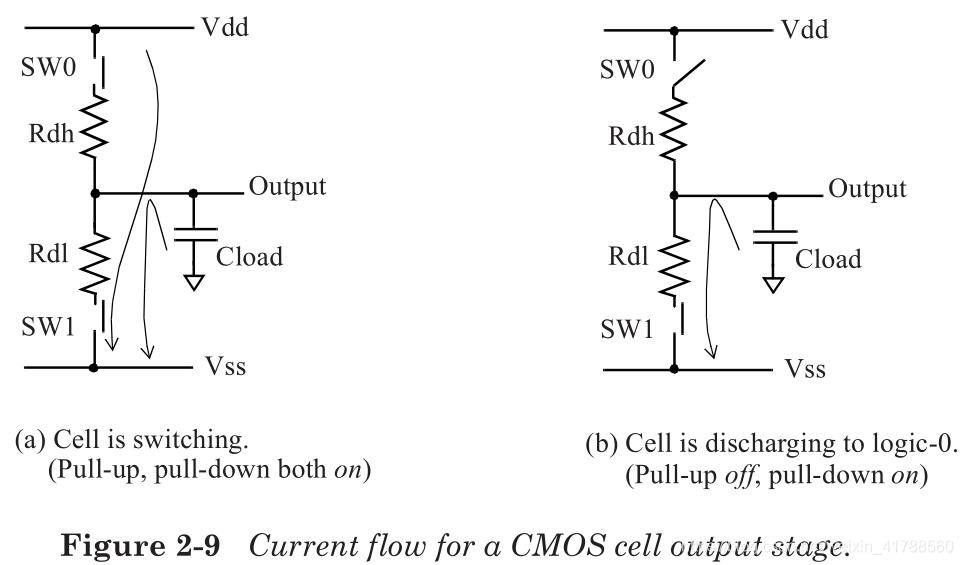

在 CMOS 单元中,输出端充电和放电波形与图 2-8 中的 RC 充电和放电波形不同,因为 PMOS 上拉和 NMOS 下拉晶体管在短时间内同时导通。图 2-9 显示了 CMOS 反相器单元内输出从逻辑 1 切换到逻辑 0 的各个阶段的电流路径。图 2-9(a) 显示了上拉和下拉结构都打开时的电流。 之后,上拉结构关闭,电流如图 2-9(b) 所示。输出达到最终状态后,由于电容 Cload 已完全放电,因此没有电流流动。

图 2-10(a) 显示了 CMOS 单元输出端的代表性波形。请注意过渡波形如何逐渐向 Vss 轨道和 Vdd 轨道弯曲,波形的线性部分位于中间。

在本文中,我们将使用如图 2-10(b) 所示的简单绘图来描绘一些波形。它显示了具有一些转换时间的波形,即从一种逻辑状态转换到另一种逻辑状态所需的时间。图2-10(c)示出了使用0跃迁时间的相同波形,即理想波形。我们将在本文中交替使用这两种形式来解释这些概念,但实际上,每个波形都有其真实的边缘特征,如图 2-10(a) 所示。

传播延迟(Propagation Delay)

考虑一个 CMOS 反相器单元及其输入和输出波形。单元的传播延迟是根据开关波形上的一些测量点定义的。这些点是使用以下四个变量定义的:

1 | # 输入下降沿的阈值点: |

这些变量是用于描述单元库的命令集的一部分(该命令集在 Liberty中进行了描述)。这些阈值规格以 Vdd 或电源的百分比表示。大多数标准单元库的延迟测量通常使用 50% 阈值。

上升沿是从逻辑 0 到逻辑 1 的过渡。下降沿是从逻辑 1 到逻辑 0 的转变。

以图 2-11 逆变器单元及其引脚处的波形示例。传播延迟表示为:

- 输出下降延迟 (Tf)

- 输出上升延迟 (Tr)

一般来说,这两个值是不同的。图 2-11 显示了如何测量这两个传播延迟。

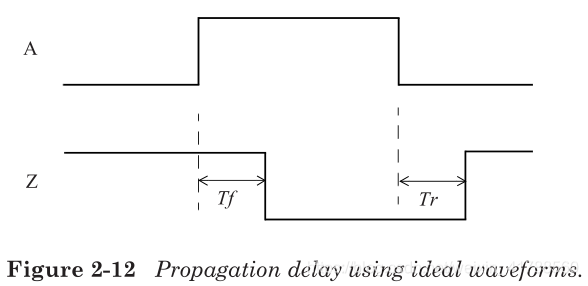

如果我们查看理想波形,传播延迟就是两个边沿之间的延迟。如图 2-12 所示。

波形转换(Slew of a Waveform)

转换速率( slew rate )被定义为变化速率。在静态时序分析中,根据过渡(transition)是慢还是快来测量上升或下降的波形。转换(slew)通常用转换时间(transition time)来衡量,即信号在两个特定电平之间转换所花费的时间。请注意,转换时间实际上与转换速率成反比——转换时间越大,转换速度越慢,反之亦然。图2-10显示了CMOS单元输出的典型波形。在两端的波形是渐近的,很难确定准确的开始和结束的过渡点。因此,转换时间是根据特定的阈值水平来定义的。例如, 转换阈值设置可以是:

1 | # Falling edge thresholds: |

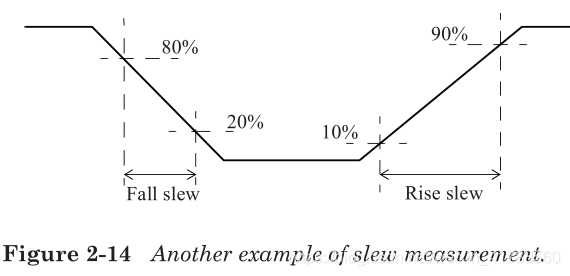

这些值被指定为Vdd的百分比。阈值设置(threshold settings)指定下降的反转为下降沿达到Vdd的70%和30%的时间差。同样地,上升设置指定上升幅度是上升边达到Vdd的30%和70%的时间差。如图2-13所示。

一个例子如图2-14显示,下降边的转换(slew)测量为20-80(80%到20%),上升边测量为10-90(10%到90%)。这里是本例的阈值设置。

1 | # Falling edge thresholds: |

信号之间的偏差(Skew between Signals)

偏差(skew)是两个或多个信号(可能是数据、时钟或两者)之间的时间差。例如,如果一个时钟树有500个端点,偏移量为50ps,则表示最长路径和最短时钟路径之间的延迟差为50ps。图2-15显示了时钟树的示例。时钟树的起点通常是定义时钟的节点。时钟树的端点通常是同步元件(如触发器 flip-flops)的时钟引脚。时钟延迟( Clock latency)是从时钟源到终点所花费的总时间。时钟偏移(Clock skew)是时钟树端点处到达时间的差异。

一个理想的时钟树是一个假设时钟源具有无限驱动的树,也就是说,时钟可以无延迟地驱动无限源。此外,假设时钟树中存在的任何单元具有零延迟。

在逻辑设计的早期阶段,STA通常使用理想的时钟树执行,因此分析的重点是数据路径。在理想的时钟树中,时钟偏移默认为0ps。可以使用set_clock_Latency命令显式指定时钟树的延迟。以下示例对时钟树的延迟进行建模:

1 | set_clock_latency 2.2 [get_clocks BZCLK] |

时钟树的时钟偏移也可以通过使用set_Clock_INDUCTION命令显式指定其值来表示:

1 | set_clock_uncertainty 0.250 -setup [get_clocks BZCLK] |

set_clock_uncertainty指定一个窗口,在该窗口内可以出现时钟边沿。时钟边沿时序的不确定性,是为了考虑几个因素,例如时钟周期抖动( clock period jitter )和用于时序验证的附加裕度(additional margins)。每一个真实的时钟源都有一个有限的抖动——一个时钟边沿可以出现的窗口。clock period jitter由所使用的时钟发生器的类型决定。实际上,没有理想的时钟,也就是说,所有时钟都有有限的抖动,在指定时钟不确定性时,应包括时钟周期抖动。

在实现时钟树之前,时钟不确定性还必须包括实现的预期时钟偏差。

可以为建立检查( setup checks )和保持检查(hold checks)指定不同的时钟不确定性。保持检查不需要将时钟抖动包含在不确定性中,因此通常为hold指定较小的时钟不确定性值。

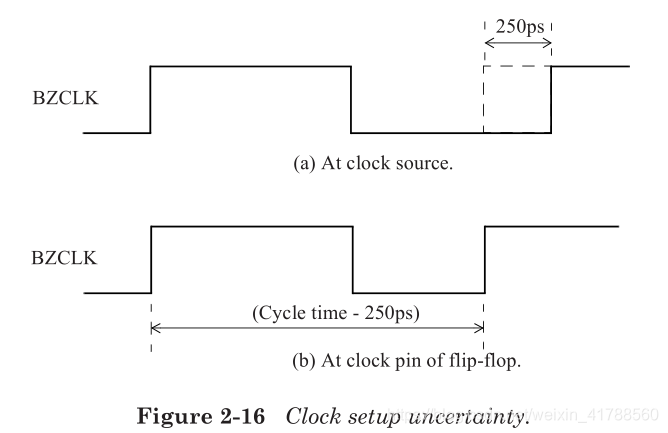

图 2-16 显示了设置不确定性为 250ps 的时钟示例。图 2-16(b) 显示在传播到下一个触发器阶段的逻辑的时间中,如何去除不确定性。这相当于验证设计以更高的频率运行。

如上所述,set_clock_uncertainty 还可用于对任何附加裕度(additional margins)进行建模。例如,设计人员可能会在设计过程中使用 50ps 的时序余量作为额外坏情况的考虑(additional pessimism)。该组件可以添加并包含在 set_clock_uncertainty 命令中。通常,在实现时钟树之前,set_clock_uncertainty 命令用于指定一个值,该值包括时钟抖动加上估计的时钟偏斜加上额外坏情况的考虑(additional pessimism)。

1 | set_clock_latency 2.0 [get_clocks USBCLK] |

稍后我们将看到 set_clock_uncertainty 如何影响建立和保持检查。最好将时钟不确定性视为最终偏斜(slack)计算的偏移量。

时序弧(Timing Arcs and Unateness)

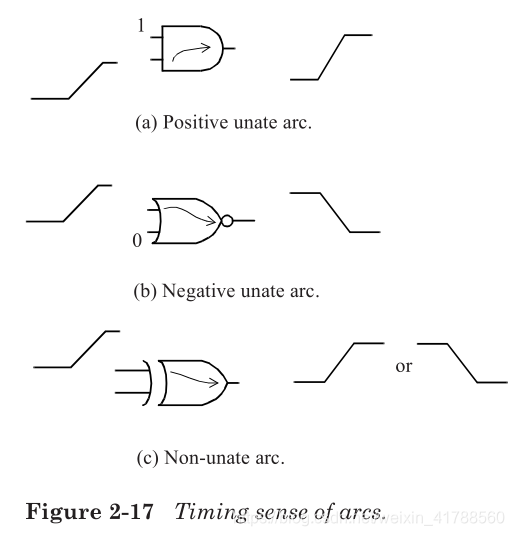

每个cell都有多个时序弧。例如,组合逻辑单元(如and、or、nand、nor 、adder单元)从单元的每个输入到每个输出具有时序弧。顺序单元(如触发器flip-flops )具有从时钟到输出的时序弧,和关于时钟的数据管脚的时序约束。每个时序弧都有一个时序感测(timing sense),即输入上不同类型的转换如何改变输出。如果输入上的上升过渡导致输出上升(或不改变),而输入上的下降过渡导致输出下降(或不改变),则为正时序弧(positive unate)。例如,and和or类型单元格的计时弧为正。见图2-17(a)。

负时序弧(negative unate)是指,输入上的上升过渡导致输出有下降过渡(或不改变)和在输入上的下降过渡,使输出具有上升过渡(或不改变)。例如,nand和nor类型单元的时序弧为负。见图2-17(b)。

在non-unate时序弧中,输出转换不能仅从输入的变化方向确定,还取决于其他输入的状态。例如,异或(xor)单元(异或)中的时序弧是non-unate的。1见图2-17(c)。

Unateness 对于时序非常重要,因为它指定了边沿(过渡transitions)如何在单元格中传播以及它们如何在单元格的输出中显示。

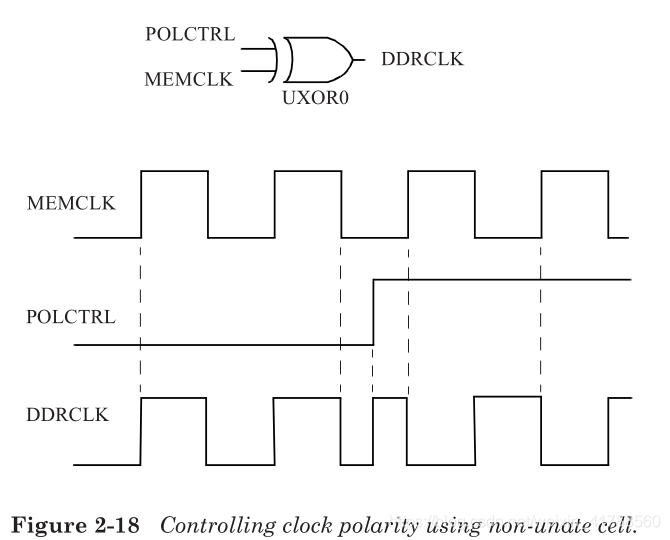

人们可以利用时序弧的non-unateness性,例如当使用异或(xor )单元时,翻转时钟的极性。参见图2-18中的示例。如果输入POLCTRL为逻辑-0,则单元UXOR0输出上的时钟DDRCLK与输入时钟MEMCLK具有相同的极性。如果POLCTRL是逻辑1,则单元UXOR0输出上的时钟与输入时钟MEMCLK的极性相反。

最小和最大时序路径(Min and Max Timing Paths)

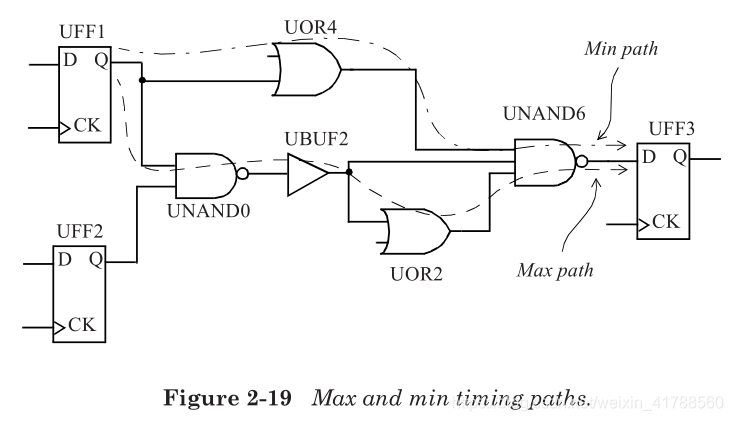

逻辑通过逻辑路径传播的总延迟称为路径延迟(path delay)。这相当于通过路径上各种逻辑单元和网络的延迟之和。通常,逻辑可以通过多条路径传播到所需的目标点。实际路径取决于逻辑路径上其他输入的状态。如图 2-19 示例。由于到达目的地的路径有多条,因此可以得到到达目的点的最大时间和最小时间。最大时间和最小时间对应的路径分别称为最大路径和最小路径。两个端点之间的最大路径是具有最大延迟的路径(也称为最长路径)。同样地,最小路径是延迟最小的路径(也称为最短路径)。

数据路径示例如图2-19所示。UFF1和UFF3之间的最大路径假定是通过UNAND0、UBUF2、UOR2和UNAND6单元的路径。UFF1和UFF3之间的最小路径被认为是通过UOR4和UNAND6单元的路径。注意,在这个例子中,最大值和最小值是与目的点(即触发器UFF3的D引脚)相关的。

最大路径通常被称为late path,而最小路径通常被称为early path。

当考虑从UFF1到UFF3等触发器到触发器路径时,其中一个触发器启动数据,另一个触发器捕获数据。在本例中,由于UFF1启动数据,因此UFF1被称为启动触发器。因为UFF3捕获数据,所以UFF3被称为捕获触发器。请注意,启动和捕获术语总是与触发器到触发器路径有关。例如,UFF3将成为通往捕获UFF3产生的数据的触发器路径的启动触发器。

时钟域(Clock Domains)

在同步逻辑设计中,一个周期时钟信号锁存计算到触发器中的新数据。新的数据输入是基于前一个时钟周期的触发器值。因此,锁存数据用于计算下一个时钟周期的数据。

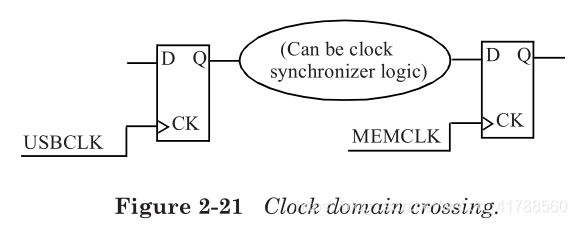

一个时钟通常为多个触发器服务。由一个时钟服务的一组触发器称为其时钟域。在典型设计中,可能存在多个时钟域。例如,200个触发器可以由USBCLK计时,1000个触发器可以由时钟MEMCLK馈送。图2-20描述了触发器和时钟。在本例中,我们说有两个时钟域。

一个令人感兴趣的问题是时钟域是彼此相关还是相互独立。答案取决于是否存在从一个时钟域开始并在另一个时钟域结束的任何数据路径。如果没有这样的路径,我们可以安全地说这两个时钟域是彼此独立的。这意味着没有从一个时钟域开始并在另一个时钟域结束的定时路径。

如果确实存在跨越时钟域的数据路径(参见图2-21),则必须决定这些路径是否是真实的。真实路径的一个例子是,具有2倍速度时钟的触发器驱动到具有1倍速度时钟的触发器中。错误路径的一个例子是,设计者明确地将时钟同步器逻辑放置在两个时钟域之间。在这种情况下,即使看起来存在从一个时钟域到下一个时钟域的时序路径,它也不是真正的时序路径,因为数据不受限制在一个时钟周期内通过同步器逻辑传播。这样的路径被称为假路径(不是真实路径),因为时钟同步器确保数据正确地从一个域传递到下一个域。可以使用set_false_path规范指定时钟域之间的假路径,例如:

1 | set_false_path -from [get_clocks USBCLK] |

即使未在图2-21中描述,时钟域交叉也可能以两种方式发生,即从USBCLK时钟域到MEMCLK时钟域,以及从MEMCLK时钟域到USBCLK时钟域。这两种情况都需要在STA中正确理解和处理。

讨论时钟域之间路径的原因是什么?通常,一种设计具有大量时钟,并且在时钟域之间可以有无数条路径。识别哪些时钟域交叉是真实的,哪些时钟交叉不是真实的是时序验证工作的一个重要部分。这使设计人员能够专注于仅验证真正时序路径。

图2-22显示了时钟域的另一个示例。多路复用器选择一个时钟源——它是一个或另一个,取决于设计的操作模式。只有一个时钟域,但有两个时钟,这两个时钟被认为是互斥的,因为一次只有一个时钟是活动的。因此,在该示例中,重要的是要注意,USBCLK和USBCLKx2的两个时钟域之间永远不可能存在路径(假设多路复用器控制是静态的,并且这种路径在设计中的其他地方不存在)。

操作条件(Operating Conditions)

静态定时分析通常在特定操作条件下执行*****。操作条件定义为工艺、电压和温度(Process, Voltage and Temperature PVT)的组合。单元延迟和互连延迟是根据指定的操作条件计算的。

******STA 可以在具有不同电压的单元的设计上执行。稍后我们将看到这些是如何处理的。 STA 也可以统计执行,这在第 10 章中描述。*

半导体代工厂为数字设计提供了三种制造工艺模型:慢工艺模型、典型工艺模型和快速工艺模型。慢速和快速工艺模型代表了铸造厂制造过程的极端角落。对于稳健设计,该设计在制造过程的极端角落以及温度和电源的极端环境中得到验证。图 2-23(a) 显示了cell delays如何随工艺角变化。图 2-23(b) 显示cell delays如何随电源电压变化,图 2-23(c) 显示cell delays如何随温度变化。因此,决定用于各种静态时序分析的工作条件非常重要。

STA 使用何种操作条件的选择还取决于单元库可用的操作条件。三个标准操作条件是:

- WCS(Worst-Case Slow):过程(process)缓慢,温度(temperature)最高(比如 125C),电压(voltage)最低(比如标称 1.2V 减 10%)。对于使用低电源的纳米技术,可能还有另一个最坏情况的慢角,对应于慢工艺、最低电源和最低温度。低温下的延迟并不总是小于高温下的延时 。这是因为纳米技术降低了与电源相关的设备阈值电压(Vt)裕度。在这种情况下,在低电源条件下,轻负载电池在低温下的延迟高于高温下的延迟。对于高Vt(更高的阈值,更大的延迟)或甚至是标准Vt(常规阈值,更低的延迟)小区来说尤其如此。这种延迟在较低温度下增加的反常行为称为温度反转。见图2-23(c)。

- TYP (Typical):过程(process)是典型的,温度(temperature)是标称的(比如25C),电压(voltage)是标称的(比如1.2V)。

- BCF(Best-Case Fast):过程(process)快速,温度(temperature)最低(比如-40℃),电压(voltage)最高(比如标称1.2V加10%)。

功率分析的环境条件通常与静态定时分析的环境条件不同。对于功率分析,工作条件可能为:

- ML (Maximal Leakage):过程很快,温度最高(比如125C),电压也最高(比如1.2V加10%)。该角对应于最大泄漏功率。对于大多数设计,此角也对应于最大有功功率。

- TL (Typical Leakage):过程是典型的,温度最高(比如125C),电压为标称值(比如1.2V)。这是指大多数设计中泄漏具有代表性的情况,因为在正常操作中,由于功率损耗,芯片温度会更高。

静态定时分析基于为STA加载和链接的库。可以使用set_operating_conditions命令明确指定设计的操作条件。

1 | set_operating_conditions “WCCOM” -library mychip |

单元库在各种操作条件下可用,选择用于分析的操作条件取决于为STA加载的内容。

标准单元库(Standard Cell Library)

描述了常用库单元描述中的时序相关信息。本章仅关注与时序、串扰和功率分析相关的属性,尽管库单元包含多个属性。纳米技术中对时序的主要影响是互连。

除了时序信息外,库单元描述还包含几个属性(attributes),如单元面积和功能,这些属性与时序无关,但在RTL合成过程中相关。在本章中,我们只关注与时序和功率计算相关的属性(attributes)。

可以使用各种标准格式来描述库单元。虽然各种格式的内容基本相似,但我们已经使用Liberty语法描述了库单元示例。

本章的开始部分描述了线性和非线性时序模型(linear and the non-linear timing models ),然后是第3.7节描述的纳米技术的高级时序模型。

引脚电容(Pin Capacitance)

单元的每个输入和输出都可以指定引脚处的电容。在大多数情况下,电容仅针对单元输入而不是输出指定,即大多数单元库中的输出引脚电容为 0。

1 | pin (INP1) { |

上面的示例显示了输入 INP1 的引脚电容值的一般规范。在最基本的形式中,引脚电容被指定为单个值(在上例中为 0.5 个单位)。 (电容单位通常是皮法,并在库文件的开头指定)。单元描述还可以为rise_capacitance(0.5 个单位)和fall_capacitance(0.45 个单位)指定单独的值,它们指的是用于引脚INP1 上的上升和下降转换的值。也可以将rise_capacitance 和fall_capacitance 值指定为一个范围,并在说明中指定下限和上限值。

时序建模(Timing Modeling)

单元时序模型旨在为设计环境中单元的各种实例提供准确的时序。时序模型通常是从单元的详细电路模拟中获得,以模拟单元运行的实际场景。为单元的每个时序弧指定时序模型。

让我们首先考虑一个简单的逆变器逻辑单元的时序弧,如图3-1所示,因为它是一个逆变器,在输入端的上升(下降)转变导致输出处的下降(上升)转变。单元的两种延迟特性是:

- Tr:输出上升延迟

- Tf:输出下降延迟

请注意,延迟是基于单元库中定义的阈值点来测量的(参见第2.4节),通常为50%Vdd。因此,从输入超过其阈值点到输出超过其阈值点,测量延迟。

通过逆变器单元的时序电弧延迟取决于两个因素:

- 输出负载(output load),即逆变器输出引脚的电容负载。

- 输入端信号的转换时间(transition time)。

延迟值与负载电容直接相关——负载电容越大,延迟越大。在大多数情况下,延迟随着输入转换时间的增加而增加。在某些情况下,输入阈值(用于测量延迟)与单元的内部开关点有显着差异。在这种情况下,通过单元的延迟可能会表现出相对于输入转换时间的非单调行为 - 较大的输入转换时间可能会产生较小的延迟,尤其是在输出负载较轻的情况下。

单元输出的转换(slew)主要取决于输出电容——输出转换时间随着输出负载的增加而增加。因此,根据单元类型及其输出负载,输入处的大转换(大转换时间)可以改善输出处。图 3-2 显示了单元输出的转换时间可以根据单元输出的负载而改善或恶化的情况。

线性时序模型(Linear Timing Model)

一个简单的时序模型是线性延迟模型,其中单元的延迟和输出转换时间表示为两个参数的线性函数:输入转换时间和输出负载电容。通过单元的延迟 D 的线性模型的一般形式如下所示。

其中 D0、D1、D2 是常数,S 是输入转换时间,C 是输出负载电容。线性延迟模型在亚微米技术的输入转换时间和输出电容范围内不准确因此,大多数单元库目前使用更复杂的模型,例如非线性延迟模型。

非线性延迟模型(Non-Linear Delay Model)

大多数单元库都包含表(table)模型,用于指定单元的各种时序弧的延迟和时序检查。一些用于纳米技术的较新的时序库还提供了基于电流源的高级时序模型(例如 CCS、ECSM 等),本章稍后将对其进行介绍。table型称为 NLDM(非线性延迟模型),用于延迟、输出转换或其他时序检查。

table模型捕获了通过单元输入引脚的输入转换时间和单元输出的总输出电容的各种组合的延迟。

延迟的 NLDM 模型以二维形式呈现,两个独立变量是输入转换时间(nput transition time )和输出负载电容(output load capacitance),table中的条目表示延迟。以下是典型逆变器单元的此类table示例:

1 | pin (OUT) { |

在上面的示例中,描述了输出引脚 OUT 的延迟。单元描述的这一部分包含从引脚 INP1 到引脚 OUT 的时序弧的上升和下降延迟模型,以及引脚 OUT 上的 max_transition 允许时间。上升和下降延迟(对于输出引脚)有单独的模型,它们分别标记为 cell_rise 和 cell_fall。索引的类型和表查找索引的顺序在查找表模板 delay_template_3x3 中描述。

1 | lu_table_template(delay_template_3x3) { |

此查找表模板指定表中的第一个变量是输入转换时间,第二个变量是输出电容。表值像嵌套循环一样指定,其中第一个索引 (index_1) 是外部(或变化最小)变量,第二个索引 (index_2) 是内部(或变化最大)变量,依此类推。每个变量有三个条目,因此它对应于一个 3×3 表。在大多数情况下,表的条目也像表一样格式化,然后可以将第一个索引 (index_1) 视为行索引,而第二个索引 (index_2) 变得等效于列索引。索引值(例如 1000)是虚拟占位符,它们被 cell_fall 和 cell_rise 延迟表中的实际索引值覆盖。指定索引值的另一种方法是在模板定义中指定索引值,而不是在 cell_rise 和 cell_fall 表中指定它们。这样的模板看起来像这样:

1 | lu_table_template(delay_template_3x3) { |

根据延迟表,0.3ns 的输入下降转换时间和 0.16pf 的输出负载将对应于 0.1018ns 的反相器上升延迟。由于输入端的下降跃迁导致逆变器输出上升,上升延迟的表查找涉及反相器输入处的下降转换。

这种在表格中将延迟表示为两个变量(转换时间和电容)的函数的形式称为非线性延迟模型,因为延迟随输入转换时间和负载电容的非线性变化在此类表中表示。

表模型也可以是 3 维的——一个例子是具有互补输出 Q 和 QN 的触发器,这在第 3.8 节中进行了描述。

NLDM 模型不仅用于延迟,还用于单元输出的转换时间,其特征在于输入转换时间和输出负载。因此,有单独的二维表用于计算单元的输出上升和下降转换时间。

1 | pin (OUT) { |

有两个这样的过渡时间表:rise_transition 和fall_transition。如第 2 章所述,转换时间是根据特定的转换阈值测量的,通常是电源的 10%-90%。

如上所示,具有 NLDM 模型的逆变器单元具有下表:

- Rise delay

- Fall delay

- Rise transition

- Fall transition

给定这种单元的输入转换时间和输出电容,如图 3-3 所示,从 cell_rise 表中获得 15ps 输入转换时间(下降)和 10fF 负载的上升延迟,从20ps 输入转换时间(上升)和 10fF 负载的 cell_fall 表。

指定单元正在反转的信息在哪里?该信息被指定为时序弧的timing_sense 字段的一部分。在某些情况下,此字段未指定,但应从引脚功能派生。

对于示例反相器单元,时序弧为negative_unate,这意味着输出引脚转换方向与输入引脚转换方向相反(负)。因此,cell_rise 表查找对应于输入引脚的下降转换时间。

非线性延迟模型查找示例(Example of Non-Linear Delay Model Lookup)

本节通过示例说明表模型的查找。如果输入转换时间和输出电容对应于表条目,则表查找是微不足道的,因为时序值直接对应于表中的值。下面的示例对应于查找不对应于表中任何可用条目的一般情况。在这种情况下,使用二维内插来提供结果时序值。为表插值选择每个维度中两个最近的表索引。考虑输入转换时间为 0.15ns 和输出电容为 1.16pF 的下降转换表(上面指定的示例表)。下面再现了与二维插值相关的下降过渡表的相应部分。

1 | fall_transition(delay_template_3x3) { |

在下面的公式中,两个 index_1 值表示为 x1 和 x2;两个index_2值分别记为y1和y2,对应的表值分别记为T11、T12、T21和T22。

如果 (x0, y0) 需要查表,则通过插值获得查找值 T00,由下式给出:

这里

x01= (x0- x1) / (x2- x1)

x20= (x2- x0) / (x2- x1)

y01= (y0- y1) / (y2- y1)

y20= (y2- y0) / (y2- y1)

用 0.15 代替 index_1 和 1.16 代替 index_2 导致 fall_transition 值:

T00= 0.75 * 0.25 * 0.1937 + 0.75 * 0.75 * 0.7280 +

0.25 * 0.25 * 0.2327 + 0.25 * 0.75 * 0.7676 = 0.6043

请注意,上述等式对于内插和外推均有效 - 即当指数 (x0, y0) 位于指数的特征范围之外时。例如,对于 index_1 为 0.05 和 index_2 为 1.7 的表查找,获得下降过渡值如下:

T00= 1.25 * (-0.25) * 0.1937 + 1.25 * 1.25 * 0.7280 +

(-0.25) * (-0.25) * 0.2327 + (-0.25) * 1.25 * 0.7676

= 0.8516

阈值规格和转换时间降额(Threshold Specifications and Slew Derating)

slew(即transition time)值基于库中指定的测量阈值。大多数上一代库(0.25 毫米或更早)使用 10% 和 90% 作为压摆或转换时间的测量阈值。

选择转换阈值以对应于波形的线性部分。随着技术变得越来越精细,实际波形最线性的部分通常在 30% 到 70% 之间。因此,大多数新一代时序库将转换测量点指定为 Vdd 的 30% 和 70%。但是,由于之前测量的转换时间在 10% 到 90% 之间,因此在填充库时测量的转换时间通常在 30% 到 70% 之间加倍。这由通常指定为 0.5 的转换降额系数指定。 30% 和 70% 的转换阈值(转换降额为 0.5)导致等效的测量点为 10% 和 90%。阈值设置示例如下所示。

1 | /* Threshold definitions */ |

上述设置指定库表中的转换时间必须乘以 0.5 才能获得与转换阈值 (30-70) 设置相对应的转换时间。这意味着转换表中的值(以及相应的索引值)实际上是 10-90 个值。在表征过程中,转换是在 30-70 处测量的,库中的转换数据对应于将测量值外推到 10% 到 90% ((70 - 30)/(90 - 10) = 0.5)。

具有一组不同转换阈值设置的另一个示例可能包含:

1 | /* Threshold definitions 20/80/1 */ |

在这个 20-80 转换率阈值设置的示例中,没有指定 slew_derate_from_library(暗示默认值为 1.0),这意味着库中的转换时间数据没有降额。转换表中的值直接对应于 20-80 表征的转换值。见图 3-4 。

这是单元库中转换阈值设置的另一个示例。

1 | slew_lower_threshold_pct_rise : 20.00; |

在这种情况下,slew_derate_from_library 设置为 0.6,并且将特征转换跳变点指定为 20% 和 80%。这意味着库中的转换表数据对应于 0% 到 100% ((80 - 20)/(100 - 0) = 0.6) 外推值。如图 3-5 所示。

指定slew降额时,延迟计算期间内部使用的slew值为:

1 | library_transition_time_value * slew_derate |

这是延迟计算工具内部使用的转换,对应于特征转换阈值测量点。

时序模型——组合单元(Timing Models - Combinational Cells)

让我们考虑两个输入和单元格的时序弧。该单元格的两个时序弧都是positive_unate;因此,输入引脚上升对应于输出上升,反之亦然。

对于二输入and单元,有四种延迟:

- A -> Z: Output rise

- A -> Z: Output fall

- B -> Z: Output rise

- B -> Z: Output fall

这意味着对于 NLDM 模型,将有四个表模型用于指定延迟。类似地,也将有四个这样的表模型用于指定输出转换时间。

延迟和转换模型(Delay and Slew Models)

一个三输入 nand 单元的输入 INP1 到输出 OUT 的时序模型示例如下所示。

1 | pin (OUT) { |

在此示例中,使用两个单元延迟表 cell_rise 和 cell_fall 以及两个转换表rise_transition 和 fall_transition 来描述从 INP1 到 OUT 的时序弧的特性。输出 max_transition 值也包含在上面的示例中。

Positive or Negative Unate

如第 2.7 节所述,nand 单元示例中的时序弧为negative unate,这意味着输出引脚转换方向与输入引脚转换方向相反(负)。因此,cell_rise 表查找对应于输入引脚的下降转换时间。另一方面,通过and单元格或or单元格的时序弧是positive unate,因为输出转换与输入转换的方向相同。

通用组合块(General Combinational Block)

考虑具有三个输入和两个输出的组合块。

像这样的块可以有许多时序弧。通常,时序弧可以从块的每个输入到每个输出。如果从输入到输出的逻辑路径是non-inverting 或 positive unate,则输出具有与输入相同的极性。如果是反相逻辑路径是negative unate,则输出与输入极性相反;因此,当输入上升时,输出下降。这些时序弧表示通过块的传播延迟。

一些通过组合单元格的时序弧可以是positive unate 也可以是negative unatee。一个例子是通过两输入异或单元的时序弧。两输入异或( xor )单元的输入处的转换 可导致输出转换沿相同或相反的转换方向,具体取决于单元的另一个输入的逻辑状态。这些时序弧可以被描述为non-unate或两组不同的 positive unate 和 negative unate 时序模型,它们依赖于状态。此类依赖于状态的表在第 3.5 节中有更详细的描述。

时序模型——顺序单元(Timing Models - Sequential Cells)

考虑图 3-8 中所示的顺序单元的时序弧。

对于同步输入(synchronous inputs),例如引脚 D(或 SI、SE),有以下时序弧:

- Setup check arc (rising and falling)

- Hold check arc (rising and falling)

对于异步输入(asynchronous inputs),例如 pin CDN,有以下时序弧:

- Recovery check arc

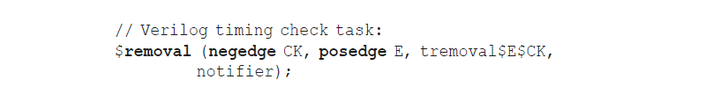

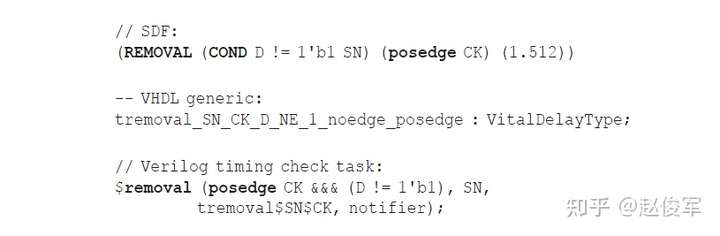

- Removal check arc

对于触发器的同步输出,例如引脚 Q 或 QN,有以下时序弧:

- CK-to-output propagation delay arc (rising and falling)

所有同步时序弧都与时钟的有效边沿有关,时钟的边沿使顺序单元捕获数据。此外,时钟引脚和异步引脚等清零,可以进行脉宽定时检查。图 3-9 显示了使用各种信号波形的时序检查。

同步检查:建立和保持(Synchronous Checks: Setup and Hold)

需要建立和保持同步时序检查,以便通过时序单元正确传递数据。这些检查验证数据输入在时钟的有效边沿是明确的,并且正确的数据在有效边沿被锁存。这些时序检查验证数据输入在活动时钟边沿附近是否稳定。当数据输入必须保持稳定时,激活时钟之前的最短时间称为建立时间(setup time)。从超过阈值的最新数据信号(通常为Vdd的50%)到超过其阈值的活动时钟边缘(通常为Vdd的50%)的时间间隔是setup time。类似地,保持时间(hold time)是数据输入必须在时钟活动边缘之后保持稳定的最短时间。从超过其阈值的活动时钟边缘到超过其阈值的最早数据信号的时间间隔是hold time。如前所述,时序单元时钟的有效边沿是导致时序单元捕获数据的上升沿或下降沿。

建立和保持检查示例(Example of Setup and Hold Checks)

顺序单元的同步管脚的setup 和hold constraints通常以二维表格的形式描述,如下所示。下面的示例显示触发器数据引脚的setup 和hold时序信息。

1 | pin (D) { |

上面的示例显示了输入管脚D上相对于顺序单元的时钟CK的上升沿的设setup 和hold constraints。二维模型是根据受约束的_-pin(D)和相关的_-pin(CK)处的过渡时间建立的。 二维查找表基于库中描述的模板setuphold_template_3x3。对于上述示例,查找表模板setuphold_template_3x3描述为:

1 | lu_table_template(setuphold_template_3x3) { |

与前面的示例一样,表中的设置值被指定为一个嵌套循环,第一个索引index_1是外部(或变化最小)变量,第二个索引index_2是内部(或变化最大)变量,依此类推。因此,当D引脚上升过渡时间为0.4ns,CK引脚上升过渡时间为0.84ns时,D引脚上升沿的设置约束为0.112ns—该值从rise_constraint 表中读取。对于D引脚的下降沿,setup constraint将检查设置表的fall_constraint表。对于过渡时间与索引值不对应的setup and hold constraint表的查找,第3.2节中描述的non-linear model查找的一般程序适用。

请注意,setup constraint的rise_constraint和fall_constraint表指的是constrained_pin。使用的时钟转换由timing_type 确定,该类型指定单元是上升沿触发还是下降沿触发。

建立和保持检查中的负值(Negative Values in Setup and Hold Checks)

请注意,上面示例中的一些hold值为负值。这是可以接受的,并且通常发生在从触发器引脚到数据内部锁存点的路径长于相应的时钟的路径时。

因此,负 hold check意味着触发器的数据管脚可以在时钟管脚之前改变,并且仍然满足hold time check。

触发器的setup值也可以为负值。这意味着在触发器的引脚上,数据可以在时钟引脚之后更改,并且仍然满足setup time check。

setup和hold都可以是负数吗?不。为使setup和hold检查一致,setup和hold值之和应为正值。因此,如果setup(或hold)检查包含负值,则相应的hold(或setup)应为正值,以便setup加上hold值为正值。有关负hold值的示例,请参见图3-10。由于setup必须在hold之前进行,因此setup加hold是一个正数。setup加hold time是要求数据信号稳定的区域宽度。

对于触发器,在扫描数据输入引脚上有一个负的hold时间是有帮助的。这在时钟偏移(clock skew)方面提供了灵活性,并且可以消除几乎所有缓冲器插入的需要,以便在scan mode中修复hold冲突(scan mode是触发器串行连接形成扫描链的模式-触发器的输出通常串行连接到下一个触发器的扫描数据输入引脚;这些连接用于测试性)。

与同步数据输入上的setup 或 hold check类似,有约束检查控制异步管脚。下面将描述这些。

异步检查(Asynchronous Checks)

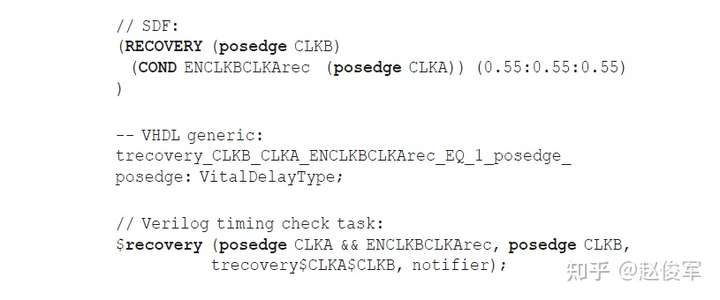

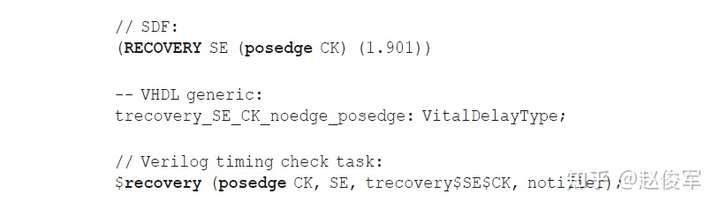

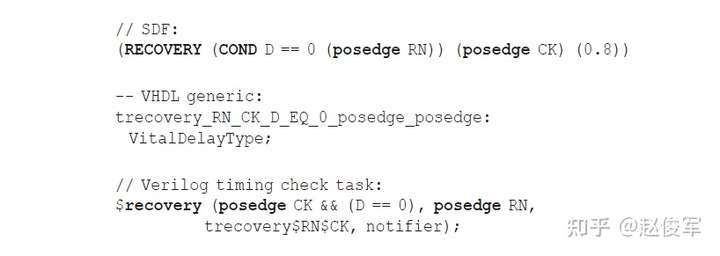

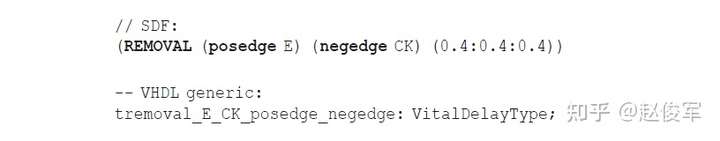

恢复和去除检查(Recovery and Removal Checks)

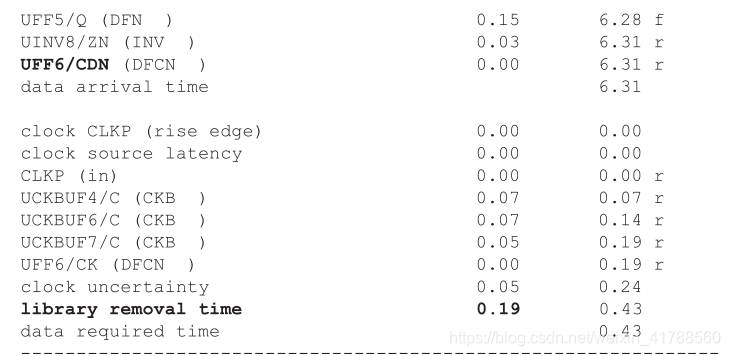

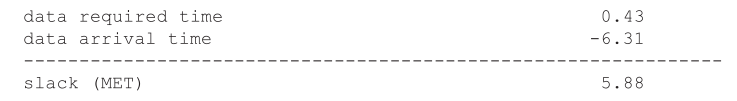

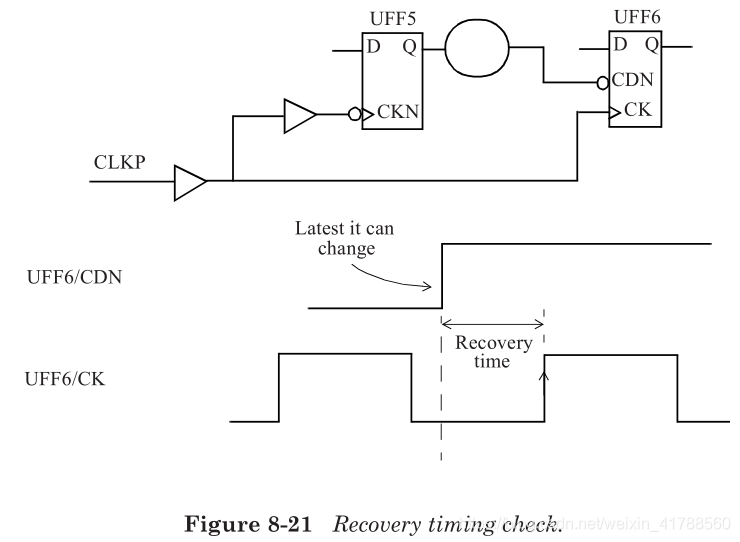

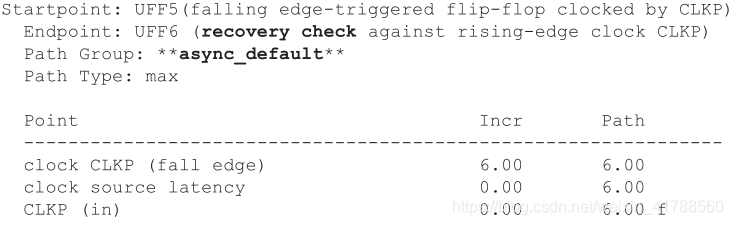

异步引脚(如Asynchronous clear或Asynchronous set)覆盖单元格的任何同步行为。当异步引脚激活时,输出由异步引脚控制,而不是由数据输入中的时钟锁存控制。但是,当异步引脚变为非活动时,时钟的活动边缘开始在数据输入中锁定。异步恢复和删除约束检查验证异步引脚在下一个活动时钟边缘已明确返回到非活动状态。

恢复时间(recovery time)是异步输入在下一个有效时钟沿之前被取消置位后稳定的最短时间。

类似地,移除时间(removal time)是有效时钟边沿之后异步引脚必须保持有效状态才能取消置位的最短时间。

异步删除和恢复检查分别在第 8.6 节和第 8.7 节中描述。

脉冲宽度检查(Pulse Width Checks)

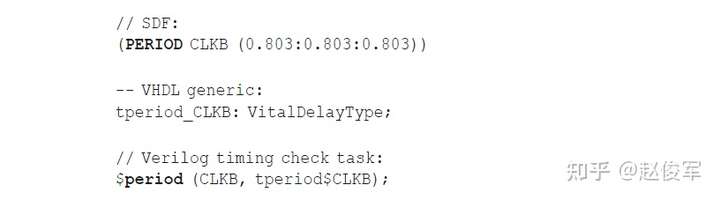

除了同步和异步时序检查之外,还有一项检查可确保单元输入引脚的脉冲宽度满足最低要求。例如,如果时钟引脚的脉冲宽度小于指定的最小值,则时钟可能无法正确锁存数据。也可以为相关的同步和异步引脚指定脉冲宽度检查。可以为高脉冲和低脉冲指定最小脉冲宽度检查。

恢复、去除和脉冲宽度检查示例(Example of Recovery, Removal and Pulse Width Checks)

下面给出了触发器异步清除引脚 CDN 的恢复时间、移除时间和脉冲宽度检查的示例。恢复和移除检查是针对时钟引脚 CK 的。由于恢复和移除检查是为置位的异步引脚定义的,因此下面的示例中仅存在上升约束。引脚 CDN 的最小脉冲宽度检查是针对低脉冲。由于 CDN 引脚为低电平有效,因此该引脚上的高脉冲宽度没有限制,因此未指定。

1 | pin(CDN) { |

传播延迟(Propagation Delay)

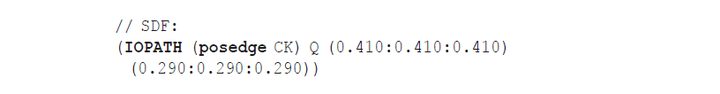

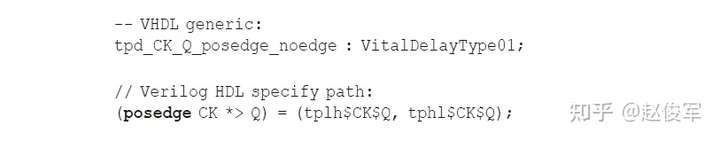

顺序单元的传播延迟是从时钟的有效边沿到输出的上升沿或下降沿。这是负边沿触发的触发器的传播延迟弧示例,从时钟引脚 CKN 到输出 Q。这是一个非同步的时序弧,因为时钟的有效边沿可能导致上升或下降输出 Q 上的边缘。这是延迟表:

1 | timing() { |

与前面的示例一样,输出延迟以输入转换时间和输出引脚电容的二维表表示。然而,在本例中,要使用的输入转换时间是 CKN 引脚的下降转换时间,因为这是一个下降沿触发的触发器。这由上面示例中的构造timing_type 指示。上升沿触发触发器将指定rising_edge 作为其timing_type。

1 | timing() { |

状态相关模型(State-Dependent Models)

在许多组合块中,输入和输出之间的时序弧取决于块中其他引脚的状态。输入和输出引脚之间的这些时序弧可以是positive unate, negative unat,或者都是positive unate弧,都是negative unat 弧。一个例子是 xor 或 xnor 单元,其中输出的时序可以是positive unate 或negative unat。在这种情况下,时序行为可能会因模块其他输入的状态而异。通常,描述了取决于引脚状态的多个时序模型。这种模型被称为状态相关模型(state-dependent models)。

XOR、XNOR 和顺序单元(XOR, XNOR and Sequential Cells)

考虑一个两输入异或单元的例子。当另一个输入 A2 为逻辑 0 时,从输入 A1 到输出 Z 的时序路径为正值。当输入 A2 为逻辑 1 时,从 A1 到 Z 的路径为负 unate。这两个时序模型是使用状态相关模型指定的。当 A2 为逻辑 0 时,从 A1 到 Z 的时序模型指定如下:

1 | pin (Z) { |

使用 when 条件指定依赖于状态的条件。虽然单元模型摘录仅说明了 cell_rise 延迟,但其他时序模型(cell_fall、rise_transition 和 fall_transition 表)也指定了相同的 when 条件。为另一个 when 条件指定单独的时序模型 - 对于 A2 为逻辑 1 的情况。

1 | timing() { |

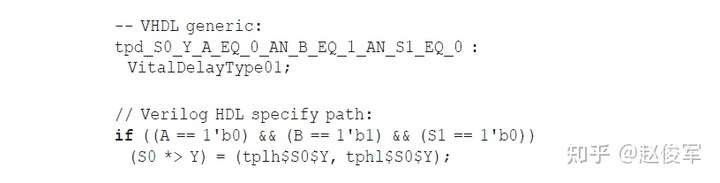

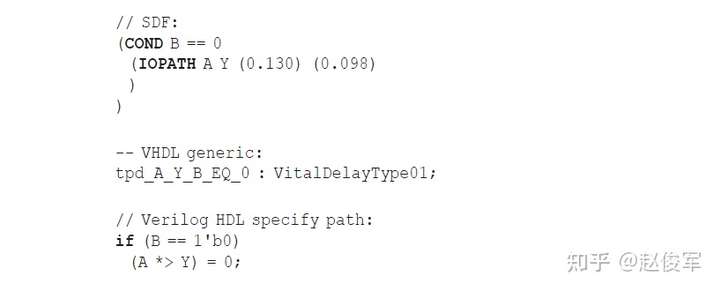

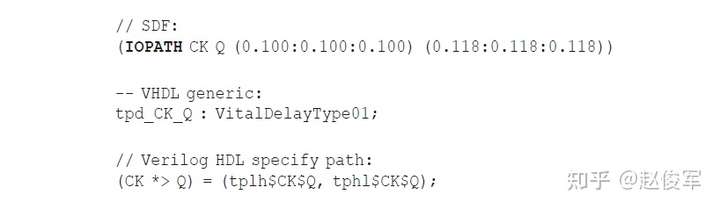

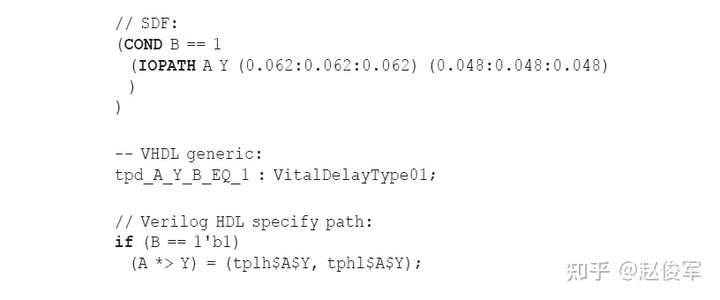

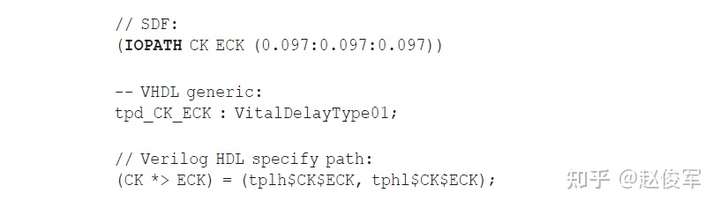

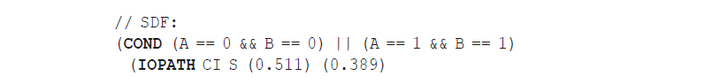

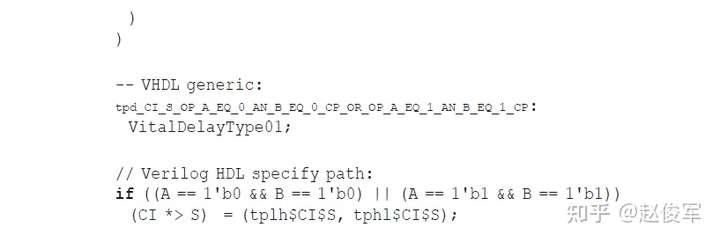

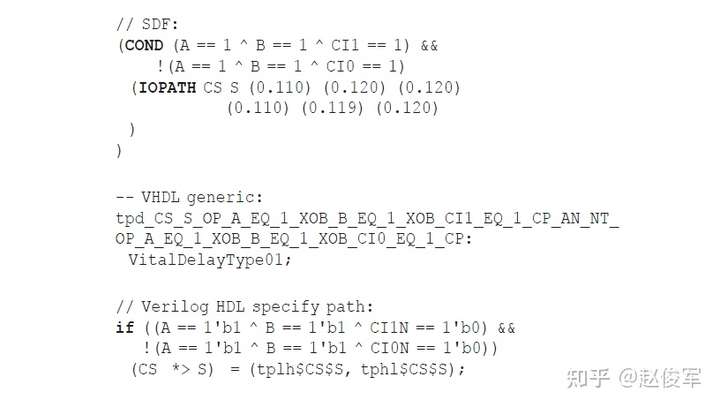

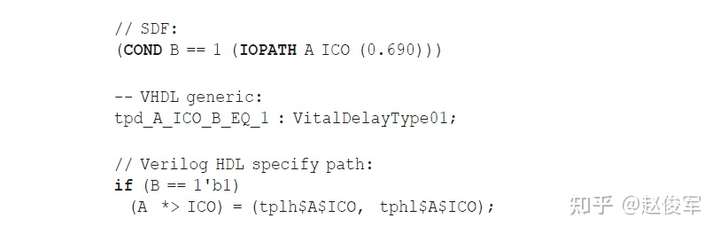

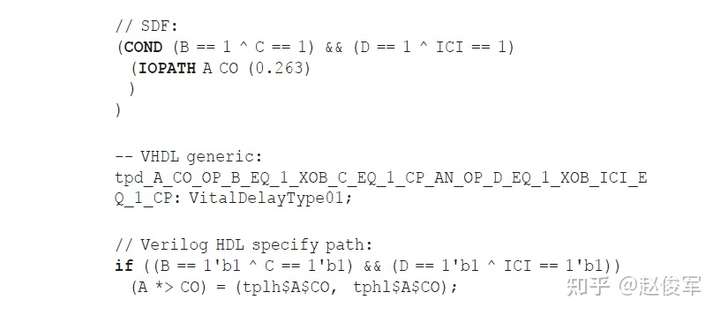

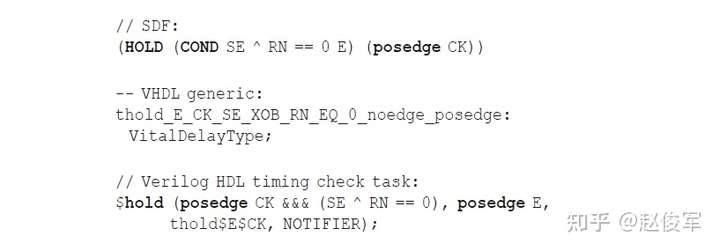

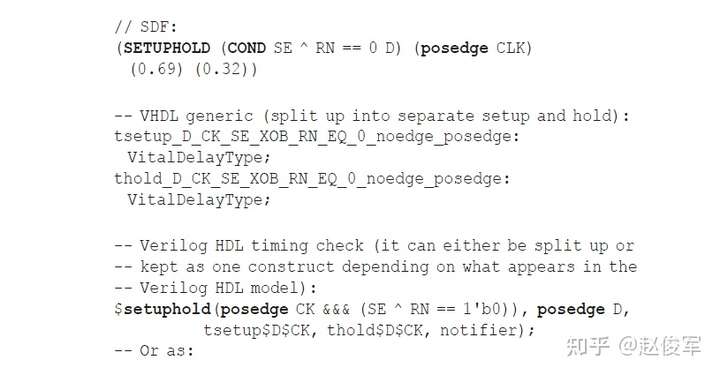

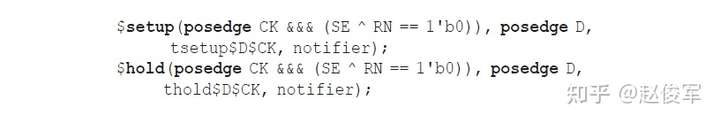

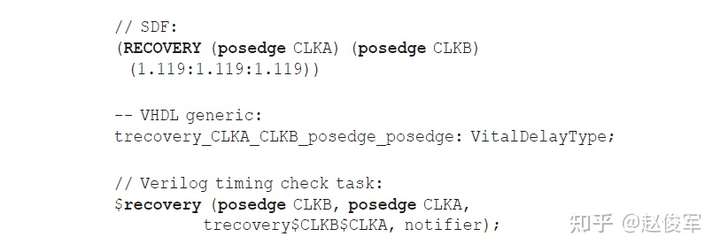

sdf_cond 用于指定生成 SDF 时要使用的计时弧的条件 - 请参阅第 3.9 节中的示例和附录 B 中描述的 COND 构造。

状态相关模型用于各种类型的时序弧。许多时序单元使用状态相关模型指定建立或保持时序约束。接下来指定使用状态相关模型进行保持约束的扫描触发器的示例。在这种情况下,指定了两组模型 - 一组在扫描启用引脚 SE 处于活动状态时,另一组在扫描启用引脚处于非活动状态时。

1 | pin (D) { |

当 SE 引脚为逻辑 0 时使用上述模型。一个类似的模型用 when 条件 SE 指定为 logic-1。

一些时序关系是使用状态相关和非状态相关模型指定的。在这种情况下,如果单元的状态已知并且包含在状态相关模型之一中,则时序分析将使用状态相关模型。如果状态相关模型不涵盖单元格的条件,则使用来自非状态相关模型的时序。考虑一种情况,其中hold constraint仅由逻辑 0 处的 SE 的一个 when 条件指定,并且没有为逻辑 1 处的 SE 指定单独的状态相关模型。在这种情况下,如果 SE 设置为逻辑 1,则使用来自非状态相关模型的保持约束。如果保持约束没有非状态依赖模型,则不会有任何 active hold constraint!

可以为时序库中的任何属性指定状态相关模型。因此,对于power,leakage power, transition time, rise and fall delays, timing constraints等,可能存在状态相关的规范。下面给出了状态相关leakage power规范的示例:

1 | leakage_power() { |

黑匣子的接口时序模型

本节介绍黑匣子(任意模块或块)的 IO 接口的时序弧。时序模型捕获黑盒 IO 接口的时序。黑盒接口模型可以具有组合以及顺序时序弧。一般来说,这些弧也可以是状态相关的。

对于图 3-11 所示的示例,时序弧可以放置在以下类别下:

- 输入到输出组合弧(Input to output combinational arc:):这对应于从输入到输出的直接组合路径,例如从输入端口 FIN 到输出端口 FOUT。

- 输入顺序弧(Input sequential arc):这被描述为连接到触发器 D 引脚的输入的建立或保持时间。通常,在连接到触发器的 D 引脚之前,模块的输入可能存在组合逻辑。这方面的一个例子是在端口 DIN 上相对于时钟 ACLK 的设置检查。

- 异步输入弧(Asynchronous input arc):这类似于触发器的输入异步引脚的恢复或移除时序约束。一个例子是触发器 UFF0 的异步清除引脚的输入 ARST。

- 输出顺序弧(Output sequential arc):这类似于时钟输出连接到触发器Q 的输出传播时序。一般来说,触发器输出和模块输出之间可以有组合逻辑。一个例子是从时钟 BCLK 到触发器 UFF1 输出到输出端口 DOUT 的路径。

除了上面的时序弧,还可以对黑匣子的外部时钟引脚进行脉宽检查。也可以定义内部节点并在这些内部节点上定义生成的时钟以及指定进出这些节点的定时弧。总之,黑盒模型可以具有以下时序弧:

- 组合逻辑路径的输入输出时序弧。

- 从同步输入到相关时钟引脚的建立和保持时序弧。

- 相关时钟引脚的异步输入的恢复和移除时序弧。

- 从时钟引脚到输出引脚的输出传播延迟。

高级时序建模(Advanced Timing Modeling)

时序模型(例如 NLDM)表示通过基于输出负载电容和输入转换时间的时序弧的延迟。实际上,电池输出看到的负载由电容和互连电阻组成。由于 NLDM 方法假设输出负载是纯电容性的,因此互连电阻成为一个问题。即使互连电阻不为零,当互连电阻的影响很小时,也可以使用这些 NLDM 模型。在存在电阻互连的情况下,延迟计算方法通过获得单元输出处的等效有效电容来改进 NLDM 模型。延迟计算工具中使用的“有效”电容方法获得等效电容,该电容在单元的输出端具有与具有 RC 互连的单元相同的延迟。有效电容方法在第 5.2 节中作为延迟计算的一部分进行了描述。

随着特征尺寸的缩小,由于波形变得高度非线性,互连电阻的影响会导致很大的不准确性。各种建模方法为单元输出驱动器提供了额外的精度。从广义上讲,这些方法通过等价电流源驱动的输出状态建模获得更高的精度。

这些方法的示例是 - CCS(Composite Current Source复合电流源)或 ECSM(Effective

Current Source Model有效电流源模型)。例如,CCS 时序模型通过使用随时间变化和电压相关的电流源为单元输出驱动器建模提供了额外的精度。通过指定不同场景下接收器引脚电容1和输出充电电流的详细模型来提供时序信息。接下来描述 CCS 模型的细节。

接收器引脚电容(Receiver Pin Capacitance)

接收器引脚电容对应于为 NLDM 模型指定的输入引脚电容。与 NLDM 模型的引脚电容不同,CCS 模型允许在转换波形的不同部分分别指定接收器电容。由于互连 RC 和等效输入非线性电容(由于来自单元内输入设备的米勒效应),接收器电容值在转换波形上的不同点发生变化。因此,该电容在波形的初始(或前导)部分与波形的尾随部分被不同地建模。

接收器引脚电容可以在引脚级别指定(如在 NLDM 模型中),其中通过该引脚的所有时序弧都使用该电容值。或者,接收器电容可以在定时弧级指定,在这种情况下,可以为不同的定时弧指定不同的电容模型。下面描述这两种指定接收器引脚电容的方法。

在引脚级别指定电容

当在引脚级别指定时,接下来给出接收器引脚电容的一维表规范示例。

1 | pin (IN) { |

index_1 指定该引脚输入转换时间的索引。一维表中的value指定了波形前导部分输入引脚处上升波形的接收器电容。

上面显示的receiver_capacitance1_rise 类似,receiver_capacitance2_rise 指定输入上升波形尾部的上升电容。下降电容(下降输入波形的引脚电容)分别由属性receiver_capacitance1_fall 和receiver_capacitance2_fall 指定。

在定时电弧级别指定电容

接收器引脚电容也可以用时序弧指定为输入转换时间和输出负载的二维表。下面给出了时序弧级别的规范示例。此示例指定了引脚 IN 波形前导部分的接收器引脚上升电容,作为输入引脚 IN 的转换时间和输出引脚 OUT 的负载的函数。

1 | pin (OUT) { |

上面的例子指定receiver_capacitance1_rise 的模型。该库包括receiver_capacitance2_rise、receiver_capacitance1_fall 和receiver_capacitance2_fall 规范的类似定义。

上面的例子指定了receiver_capacitance1_rise 的模型。该库包括receiver_capacitance2_rise、receiver_capacitance1_fall 和receiver_capacitance2_fall 规范的类似定义。

输出电流

在 CCS 模型中,非线性时序用输出电流表示。输出电流信息被指定为依赖于输入转换时间和输出负载的查找表。

输出电流针对输入转换时间和输出电容的不同组合而指定。对于这些组合中的每一个,都指定输出电流波形。本质上,这里的波形是指指定为时间函数的输出电流值。使用output_current_fall 指定的下降输出波形的输出电流示例如下所示:

1 | pin (OUT) { |

reference_time 属性是指输入波形越过延迟阈值的时间。 index_1 和 index_2 是指输入转换时间和使用的输出负载,index_3 是时间。 index_1 和 index_2(输入转换时间和输出电容)只能有一个值。 index_3 是指时间值,表值是指相应的输出电流。因此,对于给定的输入转换时间和输出负载,可以使用作为时间函数的输出电流波形。还指定了其他输入转换时间和输出电容组合的附加查找表。

使用 output_current_rise 指定的上升输出波形的输出电流的描述类似。

模型串扰噪声分析(Models for Crosstalk Noise Analysis)

本节介绍用于串扰噪声(或毛刺glitch)分析的 CCS 模型。这些被描述为 CCSN(CCS noise)模型。 CCS noise模型是结构模型,代表单元内不同的 CCB(Channel Connected Blocks通道连接块)。

什么是CCB? CCB是指单元的源漏通道连接部分。例如,单级单元(如反相器、与非单元和非单元)仅包含一个 CCB——整个单元通过使用一个通道连接区域连接。多级单元,例如和单元,或或单元,包含多个 CCB。

CCSN 模型通常指定为由单元输入驱动的第一个 CCB,以及驱动单元输出的最后一个 CCB。这些是使用稳态电流、输出电压和传播噪声模型指定的。

对于单级组合单元,如 nand 和 nor 单元,CCS 噪声模型是为每个时序弧指定的。这些单元只有一个 CCB,因此模型是从单元的输入引脚到输出引脚。

下面描述了一个 nand 单元的示例模型:

1 | pin (OUT) { |

我们现在描述 CCS noise模型的属性。属性 ccsn_first_stage 表示该模型用于 nand 单元的第一阶段 CCB。如前所述,nand cell只有一个CCB。属性 is_needed 几乎总是正确的,但对于非功能性单元(例如称重单元和天线单元)的除外。值为 both 的 stage_type 指定此阶段具有上拉和下拉结构。 miller_cap_rise 和 miller_cap_fall 分别代表上升和下降输出转换的米勒电容。

由于输入和输出端子之间的电容放大,米勒电容解释了反相级等效输入电容的增加。

直流电流(DC Current)

dc_current 表代表输入和输出引脚电压的不同组合的输出引脚上的直流电流。 index_1 指定输入电压,index_2 指定输出电压。二维表中的值指定了 CCB 输出端的直流电流。输入电压和输出电流均以库单位指定(通常为Volt 和 mA)。对于从输入 IN1 到 nand 单元的 OUT 的示例 CCS 噪声模型,-0.9V 的输入电压和 0V 的输出电压导致输出端的直流电流为 0.42mA。

输出电压(Output Voltage)

output_voltage_rise 和 output_voltage_fall 结构分别包含 CCB 输出上升和下降的时序信息。这些被指定为 CCB 输出节点的多维表。多维表被组织成多个表,指定不同input transition time和output net capacitances的上升和下降输出电压。每个表都有 index_1 指定rail-to-rail 输入转换时间速率,index_2 指定输出净电容。 index_3 指定输出电压跨越特定阈值点的次数(在本例中为 0.9V 的 Vdd 电源的 30%、70% 和 90%)。在每个多维表中,电压交叉点是固定的,在index_3中指定了CCB输出节点与电压交叉时的时间值。

传播噪声(Propagated Noise)

传播噪声高和传播噪声低模型指定多维表,这些表通过 CCB 提供噪声传播信息。这些模型表征从 CCB 输入到输出的串扰毛刺(或噪声)传播。表征在输入端使用对称三角波。传播噪声的多维表被组织成多个表,指定 CCB 输出端的毛刺波形。这些多维表包含:

- input glitch magnitude (in index_1),

- input glitch width (in index_2),

- CCB output net capacitance (in index_3), and

- time (in index_4).

CCB 输出电压(或通过 CCB 传播的噪声)在表中指定。

两级单元的噪声模型(Noise Models for Two-Stage Cells)

就像单级单元一样,两级单元(例如and cells 和 or cells)的 CCS 噪声模型通常被描述为时序弧的一部分。由于这些单元包含两个单独的 CCB,噪声模型分别为 ccsn_first_stage 和另一个为 ccsn_last_stage 指定。例如,对于双输入and单元,CCS 噪声模型由第一阶段和最后阶段的单独模型组成。这在接下来说明。

1 | pin (OUT) { |

为 IN2 指定的 ccsn_last_stage 中的模型与为 IN1 描述的 ccsn_last_stage 中的模型相同。

多级和顺序单元的噪声模型(Noise Models for Multi-stage and Sequential Cells)

复杂组合或顺序单元的 CCS 噪声模型通常作为引脚规范的一部分进行描述。这不同于单级或两级单元,如 nand、nor 和,或者 CCS 噪声模型通常在引脚对基础上指定为时序弧的一部分。复杂的多级和顺序单元通常由所有输入引脚的 ccsn_first_stage 模型和输出引脚的另一个 ccsn_last_stage 模型描述。这些单元的 CCS 噪声模型不是时序弧的一部分,但通常是为引脚指定的。

如果输入和输出之间的内部路径多达两个 CCB 级,噪声模型也可以表示为引脚对时序弧的一部分。通常,多级单元描述可以将一些 CCS 噪声模型指定为引脚对时序弧的一部分,而其他一些噪声模型可以通过引脚描述指定。

下面的示例具有使用引脚描述以及部分时序弧指定的 CCS 噪声模型。

1 | pin (CDN) { |

请注意,上面触发器单元的一些 CCS 模型是用引脚定义的。那些在输入引脚上定义的引脚规范被指定为 ccsn_first_stage,输出引脚 QN 的 CCS 模型被指定为 ccsn_last_stage。此外,两级 CCS 噪声模型被描述为 CDN 到 Q 的时序弧的一部分。因此,此示例表明单元可以将 CCS 模型指定为引脚规范的一部分和时序组的一部分。

其他噪声模型

除了上述 CCS noise模型外,一些单元库还可以提供其他模型来表征噪声。其中一些模型在 CCS noise模型出现之前就在使用了。如果 CCS noise模型可用,则不需要这些附加模型。为了完整性,我们在下面描述了一些早期的噪声模型。

DC 裕度模型(Models for DC margin):DC 裕度是指单元输入引脚允许的最大 DC 变化,它可以使单元保持稳定状态,即不会在输出端引起毛刺。例如,输入低电平的直流裕度是指输入引脚处的最大直流电压值,而不会在输出端引起任何转换。

抗噪模型(Models for noise immunity):抗噪模型指定输入引脚允许的毛刺幅度。这些通常根据以毛刺宽度和输出电容作为两个指标的二维表来描述。表中的值对应于输入引脚允许的毛刺幅度。这意味着任何小于指定幅度和宽度的毛刺都不会通过单元传播。可以指定抗噪模型的不同变体,例如:

- noise_immunity_high

- noise_immunity_low

- noise_immunity_above_high (overshoot)

- noise_immunity_below_low (undershoot).

功耗建模(Power Dissipation Modeling)

单元库包含与单元中的功耗相关的信息。这包括有功功率以及待机或泄漏功率。顾名思义,有功功率与设计中的活动有关,而待机功率是在待机模式下消耗的功率,这主要是由于泄漏造成的。

有功功率(Active Power)

有功功率与单元输入和输出引脚的活动有关。单元中的有功功率来自输出负载的充电以及内部开关。这两者通常分别称为output switching power 和 internal switching power。

输出开关功率(output switching power)与单元类型无关,仅取决于输出容性负载、开关频率和单元的电源。内部开关功率取决于单元的类型,因此该值包含在单元库中。下面描述库中内部开关电源的规格。

内部开关电源在单元库中称为 internal power。这是当单元的输入或输出有活动时单元内的功耗。对于组合电池,输入引脚转换会导致输出切换,从而产生内部开关电源。例如,只要输入切换(在输入处有上升或下降转换),逆变器单元就会消耗功率。库中的内部电源描述为:

1 | pin (Z1) { |

上例显示了从输入引脚 A 到电池输出引脚 Z1 的功耗。模板中的 2x2 表是根据引脚 A 的输入转换和引脚 Z1 的输出电容。请注意,虽然该表包括输出电容,但表中的值仅对应于内部开关,不包括输出电容的贡献。这些值代表每个开关转换(上升或下降)在电池中耗散的内部能量。这些单位源自库中的其他单位(通常电压以伏特 (V) 为单位,电容以皮法 (pF) 为单位,这映射到以皮焦 (pJ) 为单位的能量)。因此,库中的内部功率实际上指定了每次转换消耗的内部能量。

除了功率表之外,上面的示例还说明了电源引脚、接地引脚和断电功能的规范,该功能指定了电池可以断电的条件。这些构造允许在不同电源可能断电的设计和场景中使用多个电源。下图显示了每个单元的电源引脚规格。

1 | cell (NAND2) { |

电源规范语法允许单独构造上升和下降功率(指输出检测)。就像时序弧一样,功率规范也可以与状态相关。例如,异或单元的状态相关功耗可以指定为依赖于各种输入的状态。

对于组合单元,开关功率是在输入输出引脚对的基础上指定的。然而,对于具有互补输出 Q 和 QN 的触发器等时序单元,CLK->Q 转换也会导致 CLK->QN 转换。因此,库可以将内部开关功率指定为一个三维表,如下所示。下面示例中的三个维度分别是 CLK 的输入压摆和 Q 和 QN 的输出电容。

1 | pin (Q) { |

即使输出或内部状态没有转换,也可以消耗开关功率。一个常见的例子是在触发器的时钟引脚上切换的时钟。触发器在每次时钟切换时消耗功率 - 通常是由于触发器单元内部的反相器的切换。即使触发器输出不切换,时钟引脚切换引起的功率也会耗散。因此,对于时序单元,输入引脚功率是指单元内部的功耗,即输出不转换时的功耗。下面是输入引脚电源规格的示例。

1 | cell (DFF) { |

此示例显示了 CLK 引脚切换时的电源规格。这表示即使输出不切换时时钟切换导致的功耗。

时钟引脚的功率是否被重复计算了(Double Counting Clock Pin Power?)

请注意,触发器还包含由于 CLK->Q 转换引起的功耗。因此,重要的是 CLK->Q 功率规格表中的值不包括由于对应于输出 Q 不切换时的条件的 CLK 内部功率的贡献。

上述准则是指应用工具使用功率表的一致性,并确保在功率计算过程中不会重复计算由于时钟输入而指定的内部功率。

泄露功率(Leakage Power)

大多数标准单元都设计为仅在输出或状态发生变化时才耗散功率。当电池通电但没有活动时消耗的任何功率都是由于非零泄漏电流。泄漏可能是由于 MOS 器件的亚阈值电流或由于通过栅极氧化物的隧道电流。在前几代 CMOS 工艺技术中,漏电功率一直可以忽略不计,在设计过程中也不是主要考虑因素。然而,随着技术的缩小,泄漏功率变得越来越重要,与有功功率相比不再可以忽略不计。

高 Vt 单元是指阈值电压高于工艺技术标准的单元。

上所述,泄漏功率贡献来自两种现象:MOS 器件中的亚阈值电流和栅极氧化物隧穿。通过使用高 Vt 单元,可以降低亚阈值电流;然而,由于高 Vt 单元的速度降低,因此需要进行权衡。高 Vt 单元具有较小的泄漏但速度较慢。类似地,低 Vt 单元具有更大的泄漏但允许更快的速度。通过切换到高(或低)Vt 单元,栅极氧化物隧道效应不会显着改变。因此,控制泄漏功率的一种可能方式是使用高 Vt 单元。与高 Vt 和标准 Vt 单元之间的选择类似,设计中使用的单元强度是泄漏和速度之间的权衡。更高强度的单元具有更高的泄漏功率,但提供更高的速度。与电源管理相关的权衡在第 10.6 节中详细描述。

亚阈值 MOS 泄漏与温度具有很强的非线性相关性。在大多数工艺技术中,随着器件结温从 25C 增加到 125C,亚阈值泄漏会增加 10 到 20 倍。栅极氧化物隧道效应的贡献相对于温度或器件的 Vt 而言是相对不变的。在 100 纳米及以上工艺技术中可忽略不计的栅极氧化物隧道效应,已成为 65 纳米或更精细技术在较低温度下泄漏的重要因素。例如,对于 65nm 或更精细的工艺技术,栅极氧化物隧道泄漏可能等于室温下的亚阈值泄漏。在高温下,亚阈值泄漏仍然是泄漏功率的主要贡献者。

为库中的每个单元指定了泄漏功率。例如,逆变器单元可能包含以下规格:

1 | cell_leakage_power : 1.366; |

这是单元中耗散的泄漏功率 - 泄漏功率单位在库的标题中指定,通常以纳瓦为单位。通常,泄漏功率取决于单元的状态,并且可以使用 when 条件指定状态相关值。

例如,INV1 单元格可以具有以下规范:

1 | cell_leakage_power : 0.70; |

其中 I 是 INV1 单元的输入引脚。应该注意的是,规范包括一个默认值(在when条件之外),并且默认值通常是在when条件内指定的泄漏值的平均值。

单元库其他属性(Other Attributes in Cell Library)

除了时序信息之外,库中的单元描述还指定了时序弧的区域、功能和 SDF 条件。本节简要介绍了这些内容;有关更多详细信息,请参阅 Liberty 手册。

面积规格(Area Specification)

area规范提供了一个单元格或单元格组的面积。

1 | area : 2.35; |

以上指定单元格的面积为 2.35 个面积单位。这可以代表单元使用的实际硅面积,也可以是面积的相对量度。

功能规格(Function Specification)

function规范指定引脚(或引脚组)的功能。

1 | pin (Z) { |

以上指定了两个输入and单元的 Z 引脚的功能。

SDF条件(SDF Condition)

SDF 条件属性支持标准延迟格式 (SDF) 文件生成和反注释期间的条件匹配。正如when为时序分析的状态相关模型指定条件一样,SDF注释的状态相关时序使用的相应规范由sdf_cond表示。

以下示例说明了这一点:

1 | timing() { |

表征和操作条件(Characterization and Operating Conditions)

单元库指定了创建库的特征和操作条件。例如,库的标题可能包含以下内容:

1 | nom_process : 1; |

标称环境条件(指定为 nom_process、nom_temperature 和 nom_voltage)指定了表征库的过程、电压和温度。操作条件指定使用该库中的单元的条件。如果特性和工作条件不同,延迟计算时得到的时序值需要降额;这是通过使用库中指定的降额因子(k 因子)来实现的。

在不同于用于表征的条件下使用降额获得时序值会导致时序计算不准确。仅当在感兴趣的条件下表征库不可行时才采用降额程序。

什么是过程变量?(What is the Process Variable?)

与作为物理量的温度和电压不同,该过程不是可量化的量。出于数字表征和验证的目的,它可能是一种缓慢、典型或快速的过程。因此, 1.0(或任何其他值)的过程值是什么意思?答案如下。

库表征是一个耗时的过程,并且表征不同工艺角的库可能需要数周时间。过程变量设置允许使用以特定过程角为特征的库用于不同过程角的时序计算。过程的 k 因子可用于降低从特征过程到目标过程的延迟。如上所述,降额因子的使用会在时序计算过程中引入不准确性。跨工艺条件降额特别不准确,很少使用。总而言之,指定不同过程值(例如 1.0 或任何其他值)的唯一功能是允许在很少(如果曾经)使用的条件下降额。

使用K因子降额

如上所述,降额因子(称为 k 因子)用于在操作条件与特征条件不同时获得延迟。 k 因子是近似因子。库中 k 因子的示例如下所示:

1 | /* k-factors */ |

这些因素用于在延迟计算期间操作条件的过程、电压或温度与库中的标称条件不同时获得时序。请注意,k_volt 因子为负,这意味着延迟随着电压供应的增加而减少,而 k_temp 因子是正的,这意味着延迟通常随着温度的升高而增加(除了在 2.10 节中描述的表现出温度反转现象的电池)。 k 因子的使用方法如下:

1 | Result with derating = Original_value * |

例如,假设一个库在 1.08V 和 125C 下具有慢速过程模型。如果要获得 1.14V 和 100C 的延迟,则慢速工艺模型的单元上升延迟可通过下式获得:

1 | Derated_delay = Library_delay * |

假设使用了上面概述的 k_factors,则前面的等式映射为:

1 | Derated_delay = Library_delay * (1 - 0.42 * 0.06 - 0.0012 * 25) |

降额条件下的延迟计算为原始延迟的 94.48%。

库单元(Library Units)

单元描述具有库单位方面的所有值。这些单位是使用 Liberty 命令集在库文件中声明的。电压、时间、电容和电阻的单位声明如下例所示:

1 | library("my_cell_library") { |

在本文中,我们假设库时间单位以纳秒 (ns) 为单位,电压以伏特 (V) 为单位,每次跃迁的内部功率以皮焦 (pJ) 为单位,泄漏功率以纳瓦 (nW) 为单位,电容值为以皮法 (pF) 为单位,电阻值以 Kohms 为单位,面积单位为平方微米 (mm2),除非明确指定以帮助解释。

互连寄生(Interconnect Parasitics)

本章概述了处理和表示互连寄生的各种技术,用于设计的时序验证。

在数字设计中,连接标准单元和模块引脚的导线称为网络(net)。net通常只有一个驱动,而它可以驱动多个扇出单元或块。物理实现后,net可以在芯片的多个金属层上移动。不同的金属层可以有不同的电阻和电容值。对于等效电学表示,通常将net分成若干段,每个段由等效寄生参数表示。我们将互连迹线(interconnect trace)称为段的同义词,也就是说,它是特定金属层上网络的一部分。

互连RLC(RLC for Interconnect )

互连电阻来自设计实现中各种金属层和通孔中的互连走线。图 4-1 显示了穿过各种金属层和通孔的示例网络。因此,互连电阻可以被认为是单元的输出引脚和扇出单元的输入引脚之间的电阻。

互连电容的贡献也来自金属走线,包括接地电容以及相邻信号路径之间的电容。

电感是由电流回路引起的。通常,电感的影响在芯片内可以忽略,仅在封装和板级分析时考虑。在芯片级设计中,电流回路又窄又短——这意味着电流返回路径是通过靠近布线的电源或接地信号。在大多数情况下,时序分析不考虑片上电感。对片上电感分析的任何进一步描述超出了本书的范围。接下来描述互连电阻和电容的表示。

一段互连走线的电阻和电容 (RC) 理想地由分布式 RC 树表示,如图 4-2 所示。在该图中,RC 树的总电阻和电容 - 分别为 Rt 和 Ct -—对应于 Rp* L 和 Cp* L,其中 Rp、Cpare 每单位长度的走线互连电阻和电容值,L 是走线长度。 Rp、Cp 值通常从提取的各种配置的寄生参数中获得,由 ASIC 代工厂提供。

RC 互连可以用各种简化模型表示。这些在下面的小节中进行了描述。

T -model

在 T 模型表示中,总电容 Ct 建模为连接在电阻树的中间。总电阻 Rt 分为两部分(每部分都是 Rt/2),Ct连接在电阻树的中点,如图 4-3 所示。

Pi -model

在图 4-4 所示的 Pi 模型中,总电容 Ct 分为两部分(每部分为 Ct/2)并连接在电阻的任一侧。

更准确的分布RC树的表示是通过将Rt和Ct分解成多个部分得到的。对于分解成的N段,R和C的每一个中间段都是Rt/ N和Ct/ N。末端段可以按照T-model或Pi-model的概念建模。图4-5为末端段采用T-model的N段,图4-6为末端段采用Pi-model的N段。

通过对 RC 互连建模的广泛概述,我们现在描述如何在布局前阶段( pre-layout)(通过估计)或布局后阶段(post-layout)(通过详细提取)利用寄生互连。下一节描述了预布局过程中寄生互连的建模。

线载模型(Wireload Models)

在布局规划或布局之前,线载模型可用于估计电容、电阻和互连引起的面积开销。线载模型用于根据网络的扇出数量估计网络的长度。线载模型取决于块的面积,不同面积的设计可以选择不同的线载模型。线载模型还将估计的网络长度映射到电阻、电容和相应的布线面积开销。

块内的平均线长与块的大小密切相关;平均net长度随着块大小的增加而增加。图 4-7 显示,对于不同的区域(芯片或块大小),通常会使用不同的线载模型来确定寄生参数。因此,该图描绘了较小尺寸块的较小电容。

这是线载模型的示例。

1 | wire_load (“wlm_conservative”) { |

resistance是互连线单位长度的电阻值,capacitance是互连线单位长度的电容值,area是互连线单位长度的面积开销,slope是用于扇出-长度(fanout_length)表中未指定的数据点的外推斜率。

线载模型说明了如何将线的长度描述为扇出的函数。上面的例子如图 4-8 所示。对于表中未明确列出的任何扇出数,互连长度是使用具有指定斜率的线性外推法获得的。例如,扇出 8 会导致以下结果:

1 | Length = 4.1 + (8 - 5) * 0.5 = 5.6 units |

length, capacitance, resistance 和 area的单位在liberty中指定。

互连树(Interconnect Trees)

一旦确定了预布局互连的电阻和电容估计值,比如 Rwire 和 Cwire,下一个问题就是互连的结构。互连RC结构如何相对于驱动单元定位?这很重要,因为从驱动引脚到负载引脚的互连延迟取决于互连的结构。通常,互连延迟取决于路径上的互连电阻和电容。因此,此延迟可能因网络所采用的拓扑而异。

对于预布局估计,互连 RC 树可以使用以下三种不同表示法之一来表示(见图 4-9)。请注意,在三种情况中的每一种情况下,总互连长度(以及电阻和电容估计值)都相同。

- 最佳情况树(Best-case tree):

在最佳情况树中,假设目标(负载)引脚在物理上与驱动相邻。因此,在通向目标引脚的路径中,没有任何导线电阻。来自其他扇出引脚的所有导线电容和引脚电容仍充当驱动引脚上的负载。

- 平衡树( Balanced tree):

在这种情况下,假设每个目标引脚都位于互连线的单独部分。到目的地的每条路径都会看到总导线电阻和电容的相等部分。

- 最坏情况树(Worst-case tree):

在这种情况下,假设所有目标引脚都位于线路的远端。因此,每个目标引脚都会看到总导线电阻和总导线电容。

指定线载模型(Specifying Wireload Models)

使用以下命令指定线载模型:

1 | set_wire_load_model “wlm_cons” -library “lib_stdcell” |

当网络跨越层次边界时,可以根据线载模式将不同的线载模型应用于每个层次边界中网络的不同部分。这些线载模式是:

- top

- enclosed

- segmented

可以使用 set_wire_load_mode 规范指定线载模式,如下所示。

1 | set_wire_load_mode enclosed |

在top线载模式下,层次结构内的所有网络都继承顶层的线载模型,即忽略低层模块中指定的任何线载模型。因此,顶级线载模型优先。对于图 4-10 所示的示例,块 B1 中指定的 wlm_cons 线载模型优先于块 B2、B3 和 B4 中指定的所有其他线载模型。

在enclosed线载模式下,完全包围网络的块的线载模型用于整个网络。对于图 4-11 所示的示例,网络 NETQ 包含在块 B2 中,因此块 B2 的线载模型 wlm_light 用于该网络。完全包含在块 B3 中的其他网络使用 wlm_aggr 线载模型,而完全包含在块 B5 中的网络使用 wlm_typ 线载模型。

在segmented线负载模式下,网络的每段(segment)都从包含该段的块中获取其线负载模型,网络的每个部分都在该层次内使用适当的线负载模型。图4-12举例说明了一个网络NETQ,它的三段分别在三个块中。B3块中此网络的扇出互连使用wlm_aggr线负载模型,B4块中使用wlm_typ线负载模型,B2块中使用wlm_light线负载模型。

通常,根据模块的芯片面积选择线载模型。但是,这些可以根据用户的判断进行修改或更改。例如,可以为 0 到 400 之间的块区域选择线载模型 wlm_aggr,为 400 到 1000 之间的区域选择线载模型 wlm_typ,以及为 1000 或更高的区域选择线载模型 wlm_cons。线载模型通常在单元库中定义 - 但是用户也可以定义自定义线载模型。可以选择在单元库中将默认线载模型指定为:

1 | default_wire_load: "wlm_light"; |

在单元库中定义了基于面积选择线载模型的线载选择组。这是一个这样的例子:

1 | wire_load_selection (WireAreaSelGrp){ |

一个单元库可以包含许多这样的选择组。通过使用 set_wire_load_selection_group 规范,可以选择特定的一个用于 STA。

1 | set_wire_load_selection_group WireAreaSelGrp |

本节描述了在物理实现之前,即在预布局阶段期间对估计寄生参数的建模。下一节描述了从布局中提取的寄生参数的表示。

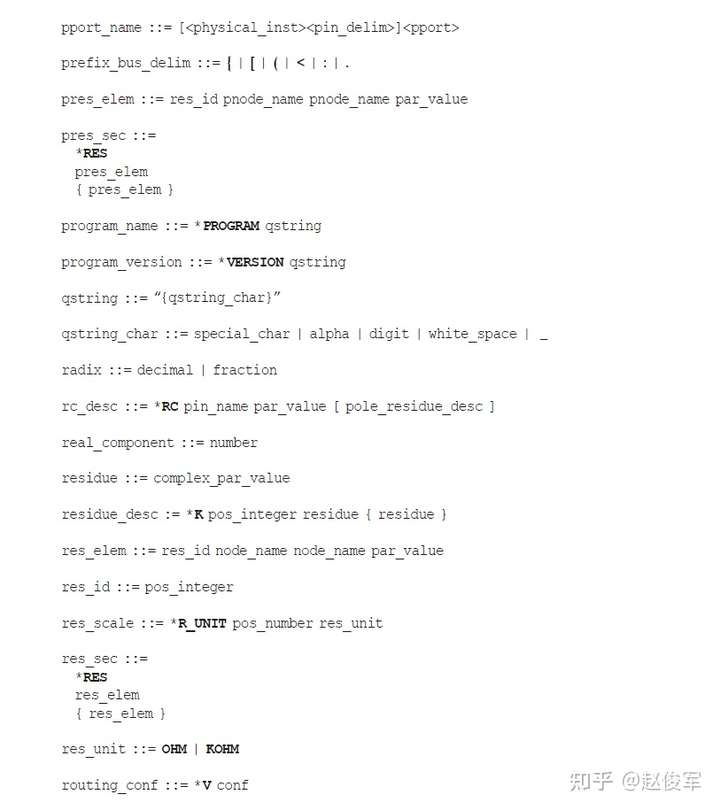

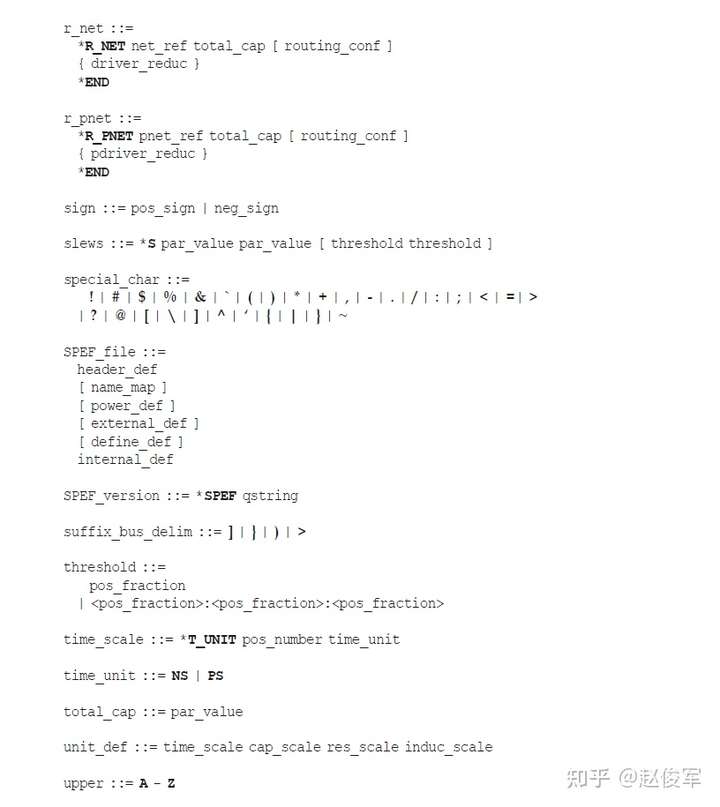

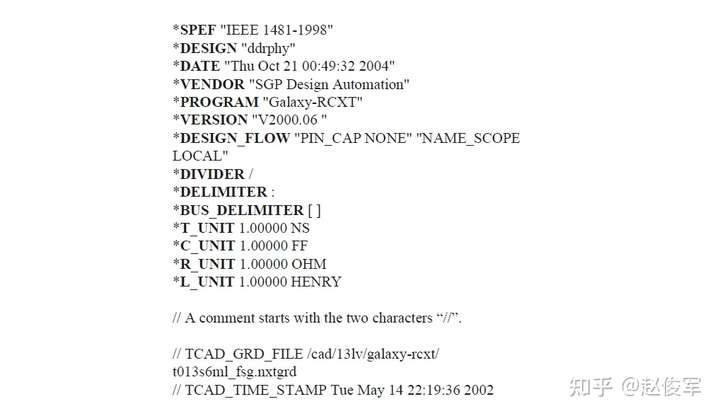

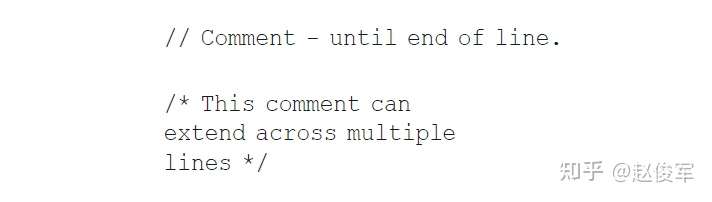

提取寄生参数的表示(Representation of Extracted Parasitics)

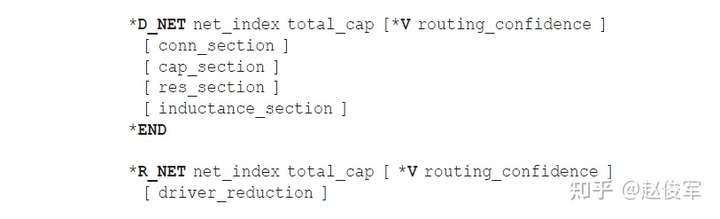

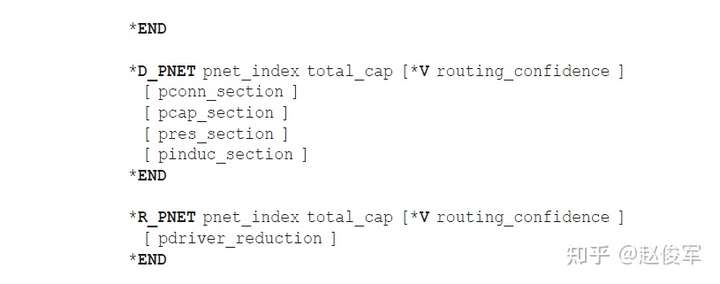

从布局中提取的寄生参数可以用三种格式描述:

- 详尽寄生参数格式 :Detailed Standard Parasitic Format(DSPF)

- 精简寄生参数格式 :Reduced Standard Parasitic Format(RSPF)

- 标准寄生参数格式 :Standard Parasitic Extraction Format(SPEF)

一些工具提供了寄生生物的专有二进制表示,如SBPF;这有助于保持较小的文件大小,并加快工具对寄生生物的读取。下面简要介绍上述三种格式。

详细标准寄生格式(Detailed Standard Parasitic Format)

电路模拟器可读的格式,如SPICE。更多信息,请参阅[NAG75]或任何关于模拟集成电路设计或模拟的书籍。

使用DSPF格式时,详尽的寄生参数以SPICE格式表示。SPICE中的Comment语句用于表明单元类型、单元引脚及其电容。电阻和电容值采用标准SPICE语法,并且单元实例也包含在此表示格式中。这种格式的优势在于,DSPF文件可以用作SPICE仿真器本身的输入。但是,缺点是DSPF语法过于详细和冗长,导致模块的总文件大小非常大。因此,这种格式在实际中仅用于相对较小的一组网络。

这里是一个示例DSPF文件,它描述了从主输入IN到缓冲器BUF的输入引脚a的互连,以及从BUF的输出引脚OUT到主输出引脚OUT的另一个网络。

1 | .SUBCKT TEST_EXAMPLE OUT IN |

DSPF中的非标准SPICE语句是以 * |开头,并具有以下格式:

1 | *|I(InstancePinName InstanceName PinName PinType PinCap X Y) |

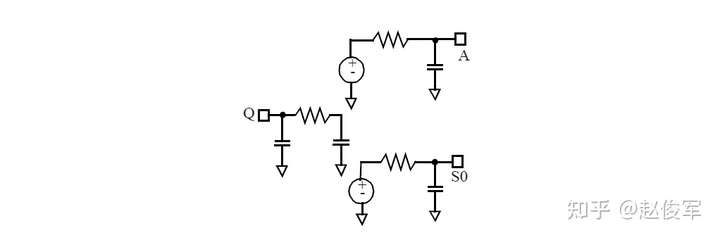

精简标准寄生格式(Reduced Standard Parasitic Format)

在RSPF表示中,寄生以简化形式表示。简化格式包括电压源和受控电流源。RSPF格式也是SPICE文件,因为它可以读入类似SPICE的模拟器。RSPF格式要求减少详细的寄生并映射到减少的格式中。因此,这是RSPF表示的一个缺点,因为寄生提取过程的重点通常是提取精度,而不是简化为类似RSPF的紧凑格式。RSPF表示的另一个限制是双向信号流不能用这种格式表示。

下面是一个RSPF文件的示例。原始设计和等效表示如图4-13所示。

1 | * Design Name : TEST1 |

此文件具有以下功能:

- 在每个扇出单元的输入引脚上都使用0.1pF的电容(C3和C4)和电阻(R2和R3)对引脚到引脚(pin-to-pin)的互连延迟进行建模,电阻值的选取原则是使RC延迟对应于引脚到引脚的互连延迟。驱动单元输出引脚上的π型负载模拟了通过该单元的延迟。

- 输入端的RC元件由理想电压源(E1和E2)驱动,该电压源等于驱动单元输出端的电压。

标准寄生交换格式(Standard Parasitic Extraction Format)

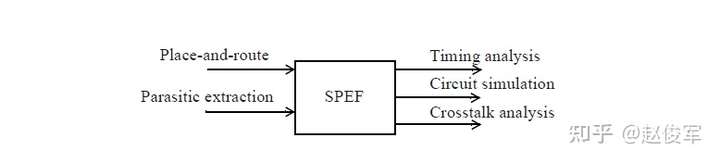

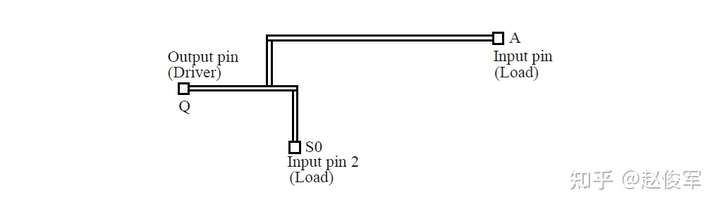

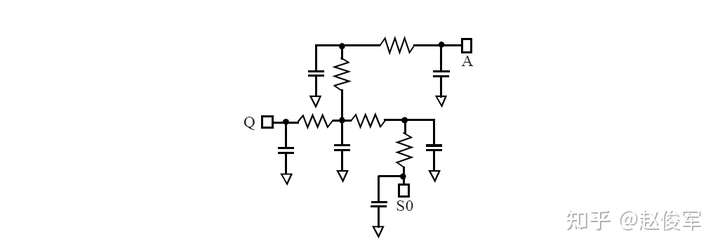

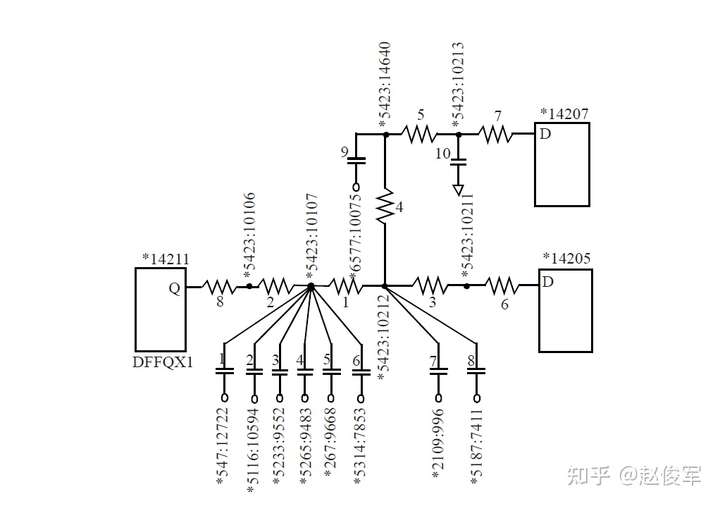

SPEF 是一种紧凑的格式,可以表示详细的寄生参数。下面显示了具有两个扇出的网络示例。

1 | *D_NET NET_27 0.77181 |

寄生参数 R 和 C 的单位在 SPEF 文件的开头指定。附录 C 中提供了对 SPEF 的更详细描述。 由于其表示的紧凑性和完整性,SPEF 是表示设计中寄生效应的首选格式。

表示耦合电容(Representing Coupling Capacitances)

上一节说明了将网络电容表示为接地电容(grounded capacitances)的情况。由于纳米技术中的大多数电容是侧壁电容(sidewall capacitances),这些电容的正确表示是信号到信号耦合电容(coupling capacitance)。

DSPF 中耦合电容的表示是原始 DSPF 标准的附加内容,因此不是唯一的。耦合电容在两组耦合网络之间复制。这意味着 DSPF 不能直接读入 SPICE,因为两组网络中的耦合电容是重复的。一些输出 DSPF 的工具通过在两个耦合网络中包含一半的耦合电容来解决这种差异。

RSPF 是简化的表示,因此不适合表示耦合电容。

SPEF 标准以统一和明确的方式处理耦合电容,因此是当对串扰时序感兴趣时选择的提取格式。此外,SPEF 是文件大小方面的紧凑表示,用于表示有和没有耦合的寄生效应。

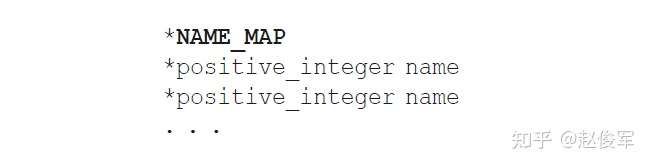

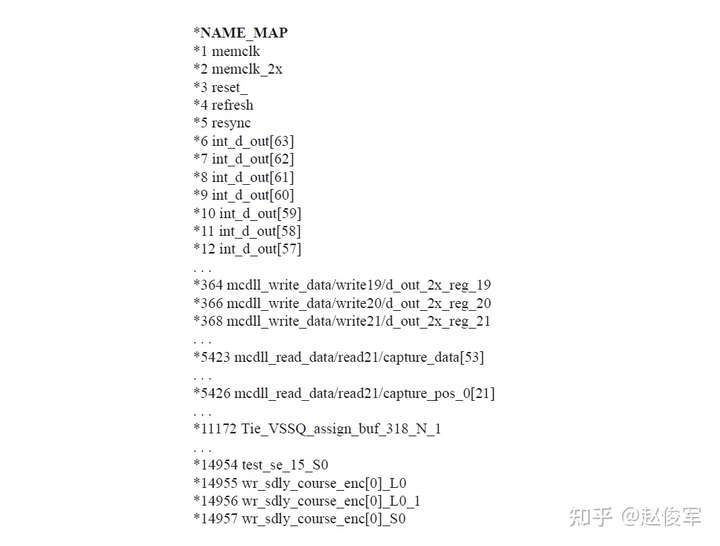

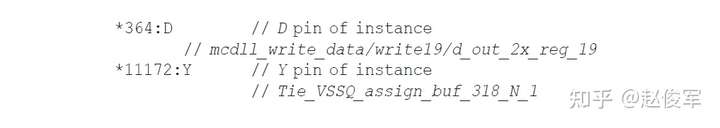

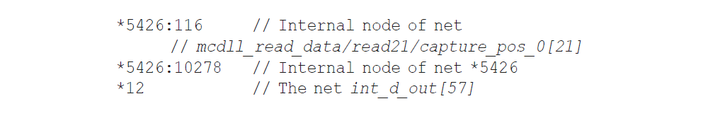

如附录 C 中所述,管理文件大小的机制之一是在文件开头设置名称目录。许多提取工具现在在 SPEF 文件的开头指定一个网络名称目录(将网络名称映射到索引),以避免重复网络名称的冗长。这显着减小了文件大小。 SPEF 的附录中显示了名称为目录的示例。

分层方法(Hierarchical Methodology)

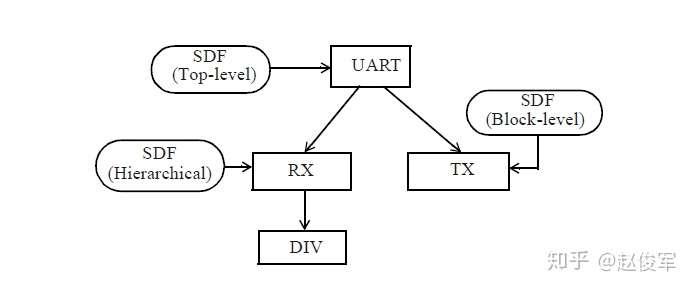

大型复杂设计在物理设计过程中通常需要分层方法来进行寄生提取和时序验证。在这种情况下,块的寄生参数在块级别被提取,然后可以在更高层次的层次结构中使用。

一个块的布局提取寄生参数可用于与布局尚未完成的另一个块的时序验证。在这种情况下,布局完整块的布局提取寄生参数通常与基于线载模型的pre-layout块的估计寄生参数一起使用。

在分层流的情况下,顶级布局已完成但块仍表示为黑盒(pre-layou),基于线载模型的寄生参数估计可用于较低级别的块以及布局提取的寄生参数最高水平。块的布局完成后,可以将顶部的布局提取寄生参数和块缝合在一起。

在布局中复制块(Block Replicated in Layout)

如果一个设计块在布局中被多次复制,则一个实例的寄生提取可以用于所有实例。这要求对于块的各种实例化,块的布局在所有方面都相同。例如,从块内布线的网络来看,布局环境应该没有区别。这意味着块级网络不与块外的任何网络电容耦合。实现这一点的一种方法是确保没有顶层网络在块上布线,并且在块边界附近布线的网络有足够的屏蔽或间距。

减少关键网络寄生效应(Reducing Parasitics for Critical Nets)

本节简要概述了管理关键网络寄生效应影响的常用技术。

降低互连电阻(Reducing Interconnect Resistance)

对于关键网络,保持低转换值(或快速转换时间)很重要,这意味着应降低互连电阻。通常,有两种方法可以实现低电阻:

- 宽走线(Wide trace):走线比最小宽度更宽可降低互连电阻,而不会导致寄生电容显着增加。因此,减少了总的 RC 互连延迟和转换时间。

- 上层(较厚)金属布线(Routing in upper (thicker) metals):上层金属层通常具有低电阻率,可用于布线关键信号。低互连电阻减少了互连延迟以及目标引脚的转换时间。

增加线距(Increasing Wire Spacing)

增加走线之间的间距会降低网络的耦合电容和总电容。大耦合电容会增加串扰,避免串扰是在相邻走线中长距离布线的网络的重要考虑因素。

相关网络的寄生参数(Parasitics for Correlated Nets)

在很多情况下,一组网络必须在时序上匹配。一个例子是高速 DDR 接口的字节通道内的数据信号。由于字节通道内的所有信号看到相同的寄生信号很重要,因此所有信号都在同一金属层中布线。例如,虽然金属层 M2 和 M3 具有相同的平均值和相同的统计变化,但这些变化是独立的,因此这两个金属层中的寄生变化不会相互跟踪。因此,如果关键信号的时序匹配很重要,那么每个金属层的布线必须相同。

延迟计算(Delay Calculation)

解释了如何为布局前和布局后时序验证计算单元延迟和路径延迟。本章扩展了前面章节中描述的概念,介绍了整个设计的时序。本章概述了用于 pre-layout 和 post-layout时序验证的基于单元设计的延迟计算。

前几章重点介绍了互连和单元库的建模。单元和互连建模技术用于获得设计时序。

概述(Overview)

延迟计算基础(Delay Calculation Basics)

典型的设计包括各种组合单元和顺序单元。我们使用图5-1所示的示例的逻辑片段来描述延迟计算的概念。

标准单元库通常不为单元输出指定引脚电容。

每个单元的库描述指定每个输入引脚的引脚电容值。因此,设计中的每个网络都有一个电容负载,它是网络中每个扇形输出的引脚电容负载加上互连的任何贡献的总和。为了简单起见,本节不考虑互连的贡献,这些贡献将在后面的章节中描述。在不考虑互连寄生的情况下,图5-1中的内部网络NET0具有由UAND1和UNOR2单元的输入引脚电容组成的网络电容。输出O1具有UNOR2单元的引脚电容加上逻辑块输出的任何电容负载。输入I1和I2具有对应于UAND1和UINV0单元的引脚电容。通过这种抽象,图5-1中的逻辑设计可以用图5-2中所示的等效表示来描述。

如第3章所述,单元库包含各种时序弧的NLDM定时模型。非线性模型表示为输入过渡时间和输出电容的二维表格。逻辑单元的输出跃迁时间也被描述为一个二维表,表示输入跃迁和网络总输出电容。因此,如果在逻辑块的输入端指定了输入转换时间(或转换slew),则可以从库单元描述中获得通过UINV0单元和UAND1单元(对于输入I1)的时序弧的输出转换时间和延迟。通过扇出单元扩展相同的方法,则可以获得通过UAND1单元的另一条时序弧(从NET0到O1)以及通过UNOR2单元的过渡时间和延迟。对于多输入单元(如UAND1),不同的输入引脚可以提供不同的输出过渡时间值。扇出网络过渡时间的选择取决于转换合并选项,如第5.4节所述。使用上述方法,可根据输入引脚的过渡时间和输出引脚的电容获得通过任何逻辑单元的延迟。

互连延迟计算(Delay Calculation with Interconnect)

预布局时序(Pre-layout Timing)

如第4章所述,在预布局时序验证期间,使用线性负载模型估算了互连寄生参数。在许多情况下,线性负载模型中的电阻贡献被设置为0。在这种情况下,线性负载贡献纯粹是电容性的,上一节中描述的延迟计算方法适用于获得设计中所有时序弧的延迟。

在线性性负载模型包括互连电阻影响的情况下,NLDM模型与单元延迟的总网络电容一起使用。由于互连是电阻式的,因此从驱动单元的输出到扇出单元的输入引脚会有额外的延迟。

布局后时序(Post-layout Timing)

金属走线的寄生参数映射到驱动单元和目标单元之间的RC网络中。使用图5-1的示例,网络的互连电阻如图5-3所示。内部网络(如图5-1中的NET0)映射到多个子节点,如图5-3所示。因此,逆变单元UINV0的输出负载由RC结构组成。由于NLDM表格是关于输入转换和输出电容的,因此输出引脚处的电阻负载意味着NLDM表格不直接适用。下一节将介绍使用具有电阻互连的NLDM。

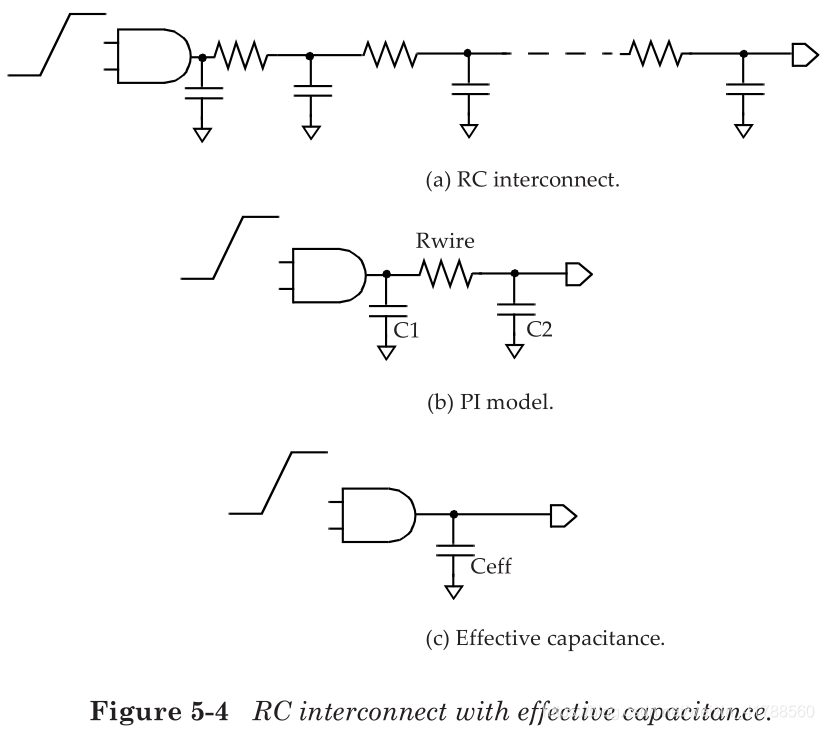

使用有效电容的单元延迟(Cell Delay using Effective Capacitance)

如上所述,当单元输出端的负载包括互连电阻时,NLDM模型不能直接使用。相反,采用“有效”电容法来处理电阻效应。

有效电容法试图找到可用作等效负载的单个电容,以便原始设计以及具有等效电容负载的设计在单元输出的定时方面表现相似。这种等效单电容被称为有效电容(effective capacitance)。

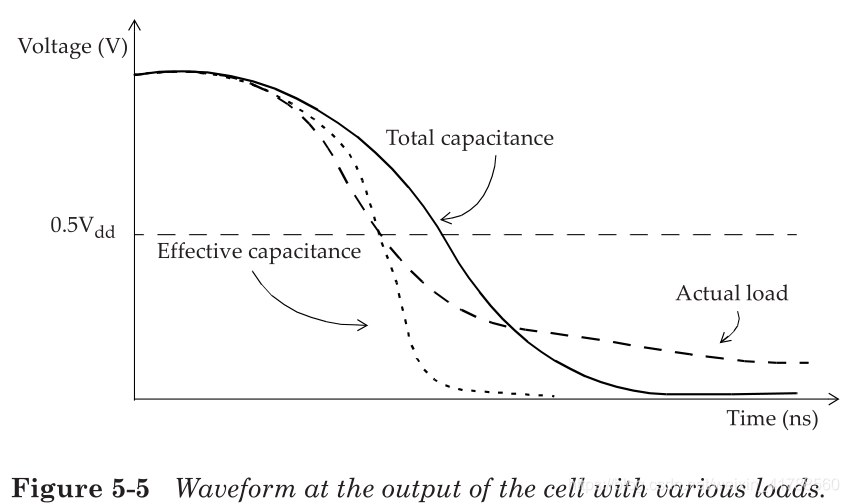

图5-4(a)所示为扇出端带有RC互连的单元。RC互连由图5-4(b)所示的等效RC PI网络表示。有效电容的概念是获得等效输出电容Ceff(如图5-4(c)所示),其通过电池的延迟与RC负载的原始设计相同。一般来说,RC负载的电池输出波形与单个电容负载的波形非常不同。

图5-5显示了总电容、有效电容和实际RC互连的单元输出波形的代表性波形。选择有效电容Ceff时,应确保图5-4(c)中单元输出端的延迟(在过渡中点测量)与图5-4(a)中的延迟相同。如图5-5所示。

关于PI等效表示,有效电容可表示为:

其中C1为近端电容,C2为远端电容,如图5-4(b)所示。k值介于0和1之间。在互连电阻可忽略不计的情况下,有效电容几乎等于总电容。这可以通过在图5-4(b)中将R设置为0来直接解释。类似地,如果互连电阻相对较大,则有效电容几乎等于近端电容C1(图5-4(b))。这可以通过将R增加到极限情况来解释,在极限情况下,R变为无穷大(本质上是一个开路)。

有效电容是以下各项的函数:

- 驱动单元

- 从驱动单元看,负载的特性或负载的输入阻抗

对于给定的互连线,输出驱动较弱的单元将比驱动较强的单元具有更大的有效电容。因此有效电容的值将介于最小值C1(对于较大的互连电阻或者较强的驱动单元)与最大值C1+C2(对于小到可忽略的互连电阻或较弱的驱动单元)之间。注意,目标引脚的转换要晚于驱动单元的输出。近端电容充电速度比远端电容快的现象也被称为互连线的电阻屏蔽效应(resistive shielding effect),因为驱动单元只能看到一部分远端电容。

与通过在库中直接查找NLDM模型计算延迟不同,延迟计算工具通过迭代程序获得有效电容。在算法方面,第一步是获得实际RC负载的单元输出所看到的驱动点阻抗。使用二阶AWE或Arnoldi算法1等任何方法计算实际RC负载的驱动点阻抗。计算有效电容的下一步是在两种情况下,将转移的电荷等效到过渡的中点。当使用实际RC负载(基于驱动点阻抗)时,电池输出处转移的电荷与使用有效电容作为负载时的电荷传输量相匹配,请注意,电荷转移仅在过渡中点之前匹配。该过程从有效电容的估计开始,然后迭代更新估计值。在大多数实际情况下,有效电容值在少量迭代内收敛。

因此,有效电容近似是计算单元延迟的良好模型。然而,使用有效电容获得的输出摆幅与电池输出的实际波形不一致。单元输出处的波形,尤其是波形后半部分的波形,不能用有效电容近似表示。请注意,在典型场景中,感兴趣的波形不在单元输出处,而是在互连的目标点处,即扇出单元的输入管脚处。

有多种方法可以计算互连终点处的延迟和波形。在许多实现中,有效电容程序还计算驱动单元的等效戴维南电压源。戴维南源由一个斜坡源和一个串联电阻Rd组成,如图5-6所示。串联电阻Rd对应于电池输出级的下拉(或上拉)电阻。

本节介绍了使用有效电容替代RC互连来计算通过驱动单元的延迟。有效电容的计算还提供了等效的戴维宁电压源模型,然后将其用于获取通过RC互连的时序。接下来将具体介绍获取通过RC互连时序信息的过程。

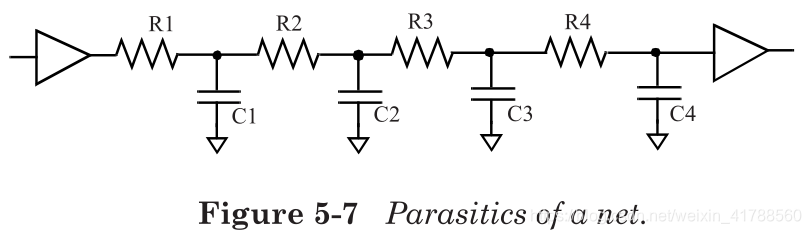

互连延迟(Interconnect Delay)

如第4章所述,网络的互连寄生通常由RC电路表示。RC互连可以是预布局或后布局。虽然布局后寄生互连可包括与相邻网络的耦合,但基本延迟计算将所有电容(包括耦合电容)视为对地电容。图5-7显示了网络及其驱动单元和扇出单元的寄生示例。

采用有效电容法,分别获得了通过驱动单元和通过互连的延迟。有效电容法通过驱动单元以及单元输出端的等效戴维南源提供延迟。然后使用戴维南源分别计算通过互连的延迟。互连部分具有一个输入和与目的地管脚一样多的输出。使用互连输入端的等效戴维南电压源,计算每个目标引脚的延迟。如图5-6所示。

在布局前进行分析时,RC互连结构由RC树类型决定,而RC互连结构又决定了互连线延迟。4.2节中已详细介绍了三种类型的RC互连树表示形式,所选的RC树类型通常在库中定义。通常,最坏情况(worst-case)的慢速库会选择最坏情况的RC树,因为该类型的树提供了最大的互连线延迟。类似地,最佳情况(best-case)的RC树结构中不包括从源引脚到目标引脚的任何电阻,通常在最佳情况的快速工艺角时被选择。因此,最佳情况RC树的互连延迟等于零。典型(typical)情况RC树和最坏情况RC树的互连延迟的处理方式与布局后RC互连一样。

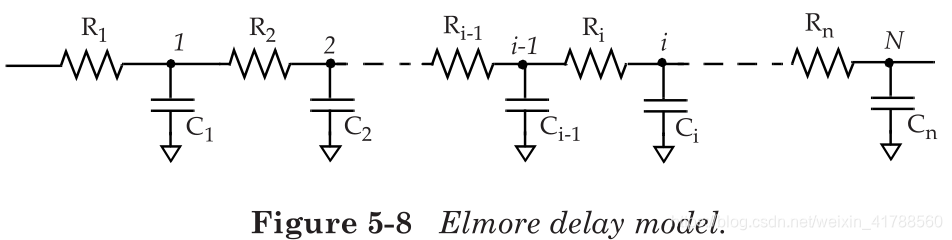

Elmore延迟

Elmore延迟适用于RC树。什么是RC树?RC树满足以下三个条件:

- 具有单个输入(源)节点。

- 没有任何电阻回路。

- 所有电容都位于节点和接地之间。

Elmore延迟可以看作是找到每段的延迟,即R与下游电容的乘积,然后取各延迟之和。

到各个中间节点的延迟表示为:

1 | Td1= C1* R1; |

Elmore延迟在数学上考虑的是脉冲响应的第一时刻。 现在,我们将Elmore延迟模型进行如下简化表示:互连线的寄生电阻与电容分别为Rwire和Cwire,互连线远端的引脚电容由负载电容Cload来建模。等效的RC网络可以简化为π模型或T模型,分别如前面章节四中图4-4和图4-3所示。两种模型都具有如下走线延迟(基于Elmore延迟方程):

这是因为Cload在其充电路径中看到整个导线电阻,而Cwire电容在T表示中看到Rwire/2,在PI表示中Cwire/2在其充电路径中看到Rwire。上述方法也可以扩展到更复杂的互连结构。

下面给出了使用带平衡RC树(以及最坏情况RC树)的线负载模型计算网络Elmore延迟的示例。

使用平衡RC树模型时,网络的电阻和电容在网络的各个分支之间平均分配(假设扇出为N)。对于具有引脚负载Cpin的分支,使用平衡RC树的延迟为:

1 | net delay = (Rwire/ N) * (Cwire/ (2 * N) + Cpin) |

使用最坏情况RC树模型时,网络的每个分支终点都考虑了网络的电阻和整个电容。此时的延迟值如下所示,这里的Cpins是所有扇出的总引脚负载:

1 | Net delay = Rwire* (Cwire/ 2 + Cpins) |

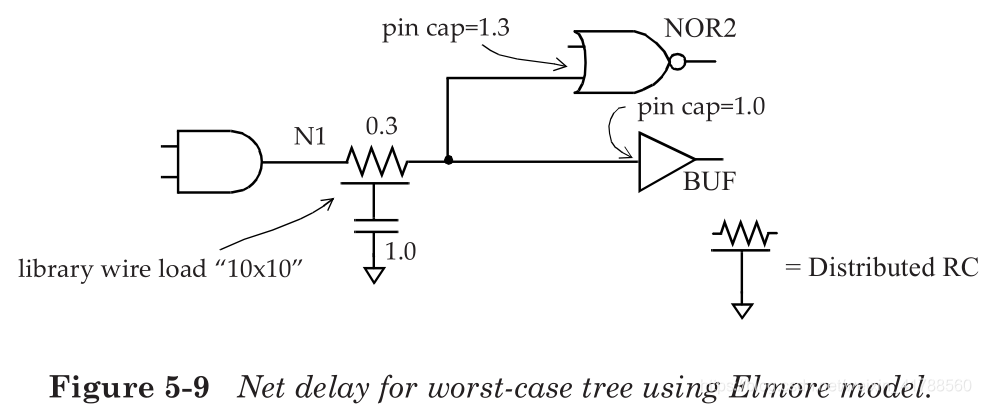

图5-9显示了一个设计示例。

如果我们使用最坏情况RC树模型来计算网络N1的延迟,我们将得到:

1 | Net delay = Rwire* (Cwire/2 + Cpins) |

如果我们使用平衡树模型,我们得到网络N1的两个分支的以下延迟:

1 | Net delay to NOR2 input pin = (0.3/2) * (0.5/2 + 1.3) |

高阶互连延迟估计(Higher Order Interconnect Delay Estimation)

如上所述,Elmore延迟是脉冲响应的第一个时刻。AWE(Asymptotic Waveform Evaluation渐近波形评估)、Arnoldi或其他方法匹配高阶响应矩。通过考虑高阶估计,可以获得更高的互连延迟计算精度。

全芯片延迟计算(Full Chip Delay Calculation)

到目前为止,本章描述了单元延迟的计算以及单元输出端的互连。因此,给定单元输入端的过渡时间,可以计算通过单元的延迟和单元输出端的互连线的延迟。互连远端(目的地或汇点)的过渡时间是下一级的输入,整个设计过程中都会重复此过程,这样就计算出了设计中每个时序弧的延迟。

转换合并(Slew Merging)

当多个转换(slew)到达一个公共点时会发生什么情况,例如在多输入单元或多驱动网络的情况下?这种公共点称为转换合并点(slew merge point)。选择哪个slew在slew merge point向前传播?考虑图5-10所示的2输入单元。

由于引脚 A 上的信号变化,引脚 Z 处的转换提前到达但上升缓慢(缓慢s转换)。由于引脚 B 上的信号变化,引脚 Z 处的转换延迟到达,但上升很快(快速转换)。在转换合并点,例如 pin Z应该选择哪个slew进行进一步传播?

根据如下所述执行的时序分析的类型(最大或最小),这些转换值中的任何一个都可能是正确的。

执行最大路径分析时有两种可能性:

- 最差转换传播(Worst slew propagation):此模式选择合并点的最差转换进行传播。这将是图5-10(A)中的slew。对于通过管脚A->Z的时序路径,此选择是精确的,但对于通过管脚B->Z的任何时序路径则是悲观的。

- 最差到达传播(Worst arrival propagation):此模式选择合并点的最差到达时间进行传播。这与图5-10(b)中的摆动相对应。在这种情况下选择的摆幅对于通过管脚B->Z的时序路径是精确的,但是对于通过管脚A->Z的时序路径是乐观的。

同样,执行最小路径分析时有两种可能性:

- 最佳转换传播(Best slew propagation):此模式选择要传播的合并点处的最佳转换。这将是图5-10(b)中的回转。对于通过管脚B->Z的定时路径,该选择是精确的,但是对于通过管脚A->Z的任何时序路径,该选择较小。对于通过A->Z的路径,路径延迟小于实际值,因此对于最小路径分析是悲观的。

- 最佳到达传播(Best arrival propagation):此模式选择合并点的最佳到达时间进行传播。这与图5-10(A)中的转换slew相对应。这种情况下选择的slew对于通过管脚A->Z的时序路径是精确的,但是选择的值大于通过管脚B->Z的定时路径的实际值。对于通过B->Z的路径,路径延迟大于实际值,因此对于最小路径分析是乐观的。

设计者可以在静态时序分析环境之外执行延迟计算以生成SDF。在这种情况下,延迟计算工具通常使用最差的转换传播(worst slew propagation)。所得到的SDF对于最大路径分析是足够的,但是对于最小路径分析可能是乐观的。

大多数静态时序分析工具使用最差和最好的转换传播作为它们的默认设置,因为它以保守的方式限制了分析。但是,在分析特定路径时,可以使用精确的转换传播。准确的转换传播可能需要在时序分析工具中启用一个选项。因此,重要的是要了解静态时序分析工具中默认使用的转换传播模式,并了解其可能过于悲观的情况。

不同的转换阈值(Different Slew Thresholds)

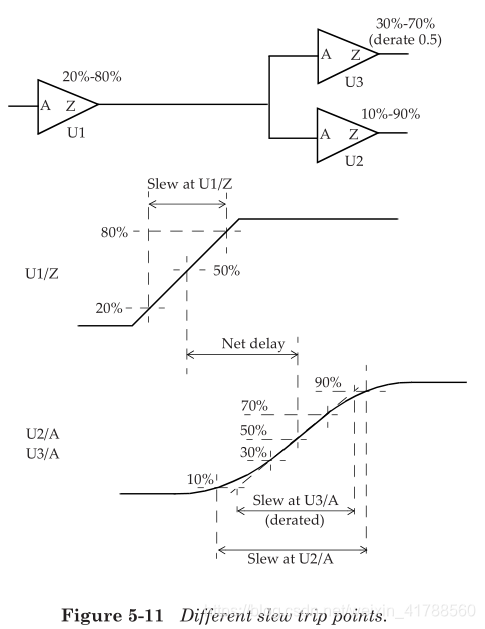

通常,库指定单元角色化过程中使用的转换(转换时间)【slew (transition time)】阈值。问题是,当具有一组转换阈值的单元驱动具有不同组转换阈值设置的其他单元时,会发生什么情况?考虑图5-11所示的情况,其中特征为20-80转换阈值的单元驱动两个扇出单元;一个转换阈值为10-90,另一个转换阈值为30-70,转换降低率为0.5。

单元格U1的转换设置在单元库中定义如下:

1 | slew_lower_threshold_pct_rise : 20.00 |

来自另一个库的单元格U2可以具有如下定义的转换设置:

1 | slew_lower_threshold_pct_rise : 10.00 |

来自另一个库的单元格U3可以具有如下定义的转换设置:

1 | slew_lower_threshold_pct_rise : 30.00 |

上面只显示了U2和U3的转换相关设置;输入和输出阈值的延迟相关设置为50%,上面没有显示。延迟计算工具根据连接网络的单元的转换阈值计算转换时间。图5-11显示了U1/Z处的转换如何与该引脚上的开关波形相对应。利用U1/Z的等效戴维南源获得扇出单元输入端的开关波形。根据U2/A和U3/A的波形及其转换阈值,延迟计算工具计算U2/A和U3/A的转换。请注意,U2/A的转换基于10-90设置,而用于U3/A的转换基于30-70设置,然后根据库中指定的slew_derate 0.5递减。此示例说明如何根据扇出单元的切换波形和转换阈值设置计算扇出单元输入端的转换时间。

在可能不考虑互连电阻的预布局(pre-layout)设计阶段时,可以按以下方式计算具有不同阈值的网络处的转换时间。例如,10%-90%转换阈值和20%-80%转换阈值之间的关系为:

1 | slew2080 / (0.8 - 0.2) = slew1090 /(0.9 - 0.1) |

因此,具有 10-90 个测量点的 500ps 转换对应于具有 20-80 个测量点的 (500ps * 0.6) / 0.8 = 375ps 转换。类似地,具有 20-80 个测量点的 600ps 转换对应于具有 10-90 个测量点的 (600ps * 0.8) / 0.6 = 800ps 转换。

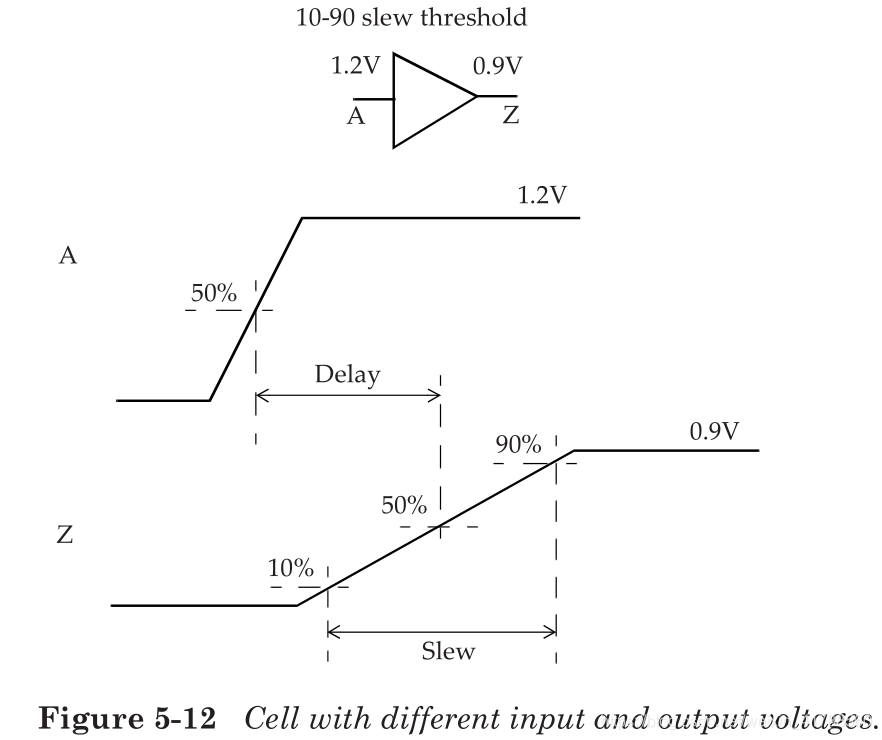

个同的电压域(Different Voltage Domains)

典型的设计可能对芯片的不同部分使用不同的电源电平。在这种情况下,电平转换单元用于不同电源域之间的接口。电平转换单元在一个电源域接受输入并在另一个电源域提供输出。例如,标准单元输入可以是 1.2V,其输出可以是降低的电源,可能是 0.9V。图 5-12 显示了一个示例

请注意,延迟是根据 50% 阈值点计算的。对于接口单元的不同引脚,这些点处于不同的电压。

路径延迟计算(Path Delay Calculation)

一旦每个时序弧的所有延迟都可用,设计中单元的时序就可以表示为时序图。通过组合单元的时序可以表示为从输入到输出的时序弧。类似地,互连由从源到每个目的地(或汇)点的相应弧表示为单独的时序弧。一旦整个设计由相应的弧线注释,计算路径延迟涉及将沿路径的所有网络和单元时序弧线相加。

组合路径延迟(Combinational Path Delay)

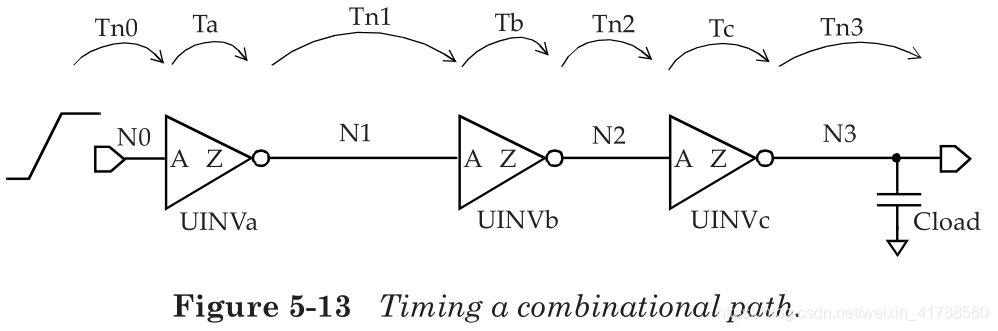

考虑串联的三个逆变器,如图 5-13 所示。在考虑从网络 N0 到网络 N3 的路径时,我们同时考虑上升沿和下降沿路径。假设在网络 N0 处有一个上升沿。

可以指定第一个逆变器输入端的 transition time (or slew);如果没有这样的规范,则假定过渡时间为 0(对应于理想步长)。输入 UINVa/A 的转换时间是通过使用上一节中指定的互连延迟模型来确定的。相同的延迟模型也用于确定网络 N0 的延迟 Tn0。

基于在UINVa的输出处的负载的RC获得在输出UINVa / Z的有效电容。然后在输入UINVa / A,并在输出UINVa / Z等效有效负荷的转换时间是用于获得单元输出下降延迟。

引脚 UINVa/Z 处的等效戴维南源模型用于通过使用互连模型确定引脚 UINVb/A 处的转换时间。互连模型还用于确定网络 N1 上的延迟 Tn1。

一旦知道输入 UINVb/A 处的转换时间,就可以类似地使用通过 UINVb 计算延迟的过程。 UINVb/Z 处的 RC 互连和 UINVc/A 引脚的引脚电容用于确定 N2 处的有效负载。 UINVb/A 的转换时间用于确定通过反相器 UINVb 的上升延迟,依此类推。

最后阶段的负载由提供的任何明确的负载规范确定,或者在没有规范的情况下仅使用网络 N3 的线负载。

上述分析假设在网络 N0 处有一个上升沿。对于网络 N0 上的下降沿的情况,可以进行类似的分析。因此,在这个简单的示例中,有两条时序路径具有以下延迟:

1 | Tfall= Tn0rise+ Tafall+ Tn1fall+ Tbrise+ Tn2rise+ Tcfall+ Tn3fall |

通常,由于驱动单元输出端的戴维南源模型不同,通过互连的上升和下降延迟可能不同。

触发器的路径(Path to a Flip-flop)

输入到触发器路径(Input to Flip-flop Path)

考虑如图5-14从输入SDT到触发器UFF1的路径的时序。

我们需要同时考虑上升沿和下降沿路径。对于输入 SDT 上升沿的情况,数据路径延迟为:

同样,对于输入 SDT 的下降沿,数据路径延迟为:

输入 MCLK 上升沿的捕获时钟路径延迟为:

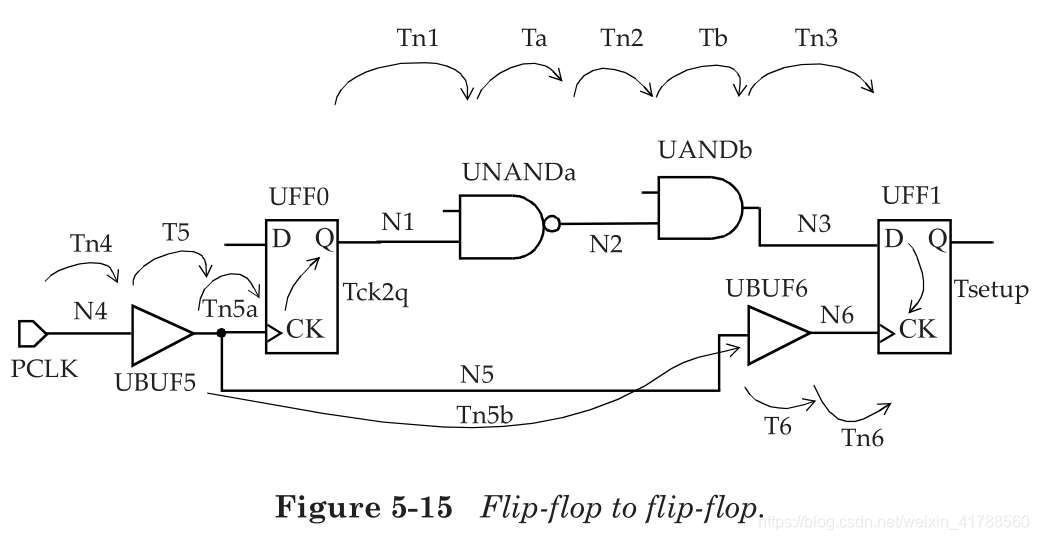

触发器到触发器路径(Flip-flop to Flip-flop Path)

图 5-15 显示了两个触发器和相应时钟路径之间的数据路径示例。

UFF0/Q 上升沿的数据路径延迟为:

输入 PCLK 上升沿的启动时钟路径延迟为:

输入 PCLK 上升沿的捕获时钟路径延迟为:

请注意,需要考虑单元的完整性,因为边缘方向在通过单元时可能会发生变化。

多路径(Multiple Paths)

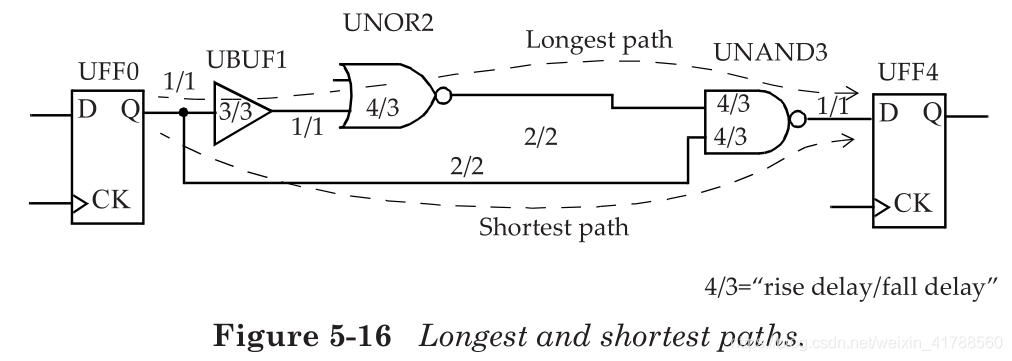

在任意两点之间,可以有许多路径。最长的路径是花费时间最长的路径;这也称为最坏路径、延迟路径或最大路径。最短的路径是需要最短时间的路径;这也称为最佳路径、早期路径或最小路径。

通过图 5-16 中的时序弧查看逻辑和延迟。两个触发器之间最长的路径是通过单元 UBUF1、UNOR2 和 UNAND3。两个触发器之间的最短路径是通过单元 UNAND3。

裕量计算(Slack Calculation)

裕量(Slack)是信号需要到达时间(Required Time)与实际到达时间(Arrival Time)之差。在图5-17中,要求数据在7ns时保持稳定才能满足建立时间(setup)要求。但是,数据在1ns时就已稳定。因此,裕量为6ns(= 7ns-1ns)。

假设所需的数据时间是从捕获触发器的设置时间获得的,

1 | Slack = Required_time - Arrival_time |

同样,如果两个信号之间的偏斜(skew)要求为100ps,并且测得的偏斜为60ps,则偏斜的裕量为40ps(= 100ps-60ps)。

串扰和噪声(Crosstalk and Noise)

在纳米技术中,串扰的影响在设计的信号完整性中起着重要作用。本章描述相关的噪声和串扰分析,即毛刺分析和串扰分析。这些技术使 ASIC 从时序的角度表现稳定运行。

在深亚微米技术中,串扰对设计的信号完整性起着重要作用。串扰噪声是指两个或多个信号之间活动的无意耦合。相关的噪声和串扰分析技术,即故障分析和串扰分析,允许在静态时序分析期间包括这些影响,本章对此进行了描述。这些技术可用于使ASIC性能稳定。

概述(Overview)

噪声(noise)是指影响芯片正常运行的非期望或无意影响。在纳米技术中,噪声会影响设备的功能或时序。

为什么会有噪声和信号完整性?

噪声在深亚微米技术中扮演重要角色的原因有几个:

- 金属层数量的增加:例如,0.25mm 或 0.3mm 工艺有四到五个金属层,在 65nm 和 45nm 工艺几何结构中增加到十个或更多金属层。图 4-1 描绘了金属互连的多层。

- 垂直主导金属纵横比:这意味着与早期工艺几何形状中的宽而细不同,线又细又高。因此,更大比例的电容由侧壁耦合电容组成,该电容映射到相邻线之间的线对线电容。

- 更精细的几何形状带来更高的布线密度:因此,在紧密的物理距离上封装了更多的金属线。

- 更多数量的交互设备和互连:因此,更多的有源标准单元和信号走线被封装在相同的硅区域中,从而导致更多的交互。

- 由于频率更高,波形更快::快速边沿速率会导致更多的电流尖峰以及对相邻迹线和单元的更大耦合影响。

- 更低的电源电压:电源电压的降低为噪声留下了很小的余量。

在本章中,我们特别研究了串扰噪声的影响。串扰噪声是指两个或多个信号之间的无意耦合活动。串扰噪声是由管芯上相邻信号之间的电容耦合引起的。这会导致网络上的开关活动对耦合信号造成意外影响。 受影响的信号称为受害者(victim),而产生影响的信号称为攻击者(aggressor)。请注意,两个耦合的网络可能会相互影响,并且通常一个网络可能既是受害者又是攻击者。

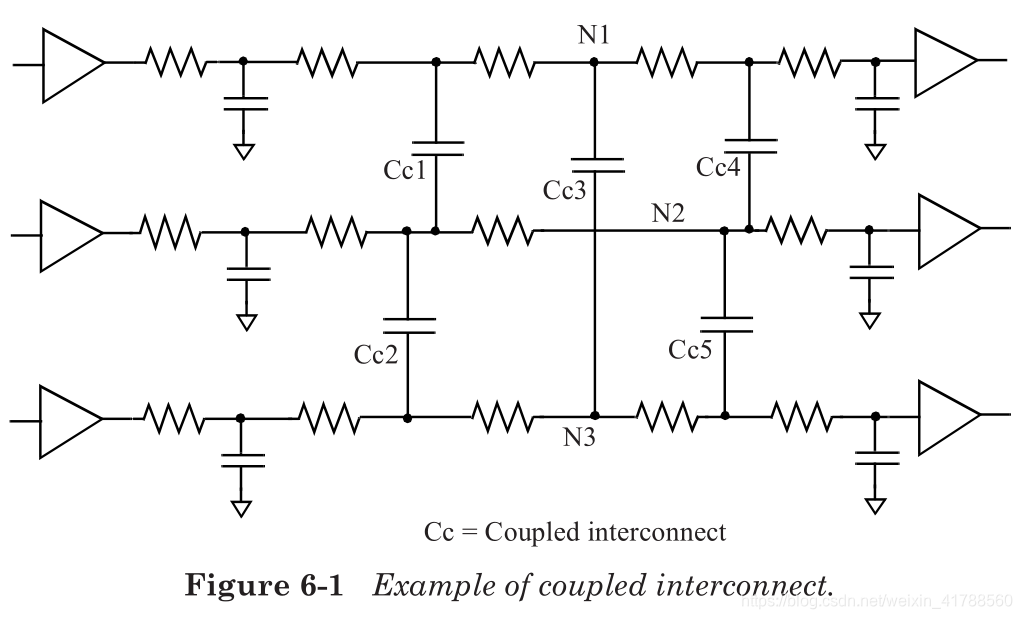

图 6-1 显示了几个信号线耦合在一起的示例。描述了耦合互连的分布式 RC 提取与几个驱动器和扇出单元。在此示例中,网络 N1 和 N2 将 Cc1 Cc4 作为它们之间的耦合电容,而 Cc2 Cc5 是网络 N2 和 N3 之间的耦合电容。

一些分析工具将毛刺(glitch)称为噪声。同样,一些工具使用串扰(crosstalk )来指代串扰对延迟的影响。

从广义上讲,串扰有两种类型的噪声影响 - 毛刺(glitch)指的是由于相邻干扰源的开关活动耦合而在稳定的受害信号上引起的噪声,以及由开关耦合引起的时序变化(串扰增量延迟)受害者的活动与攻击者的转换活动。这两种类型的串扰噪声的在接下来的两个部分进行说明。

串扰毛刺分析(Crosstalk Glitch Analysis)

基础知识(Basics)

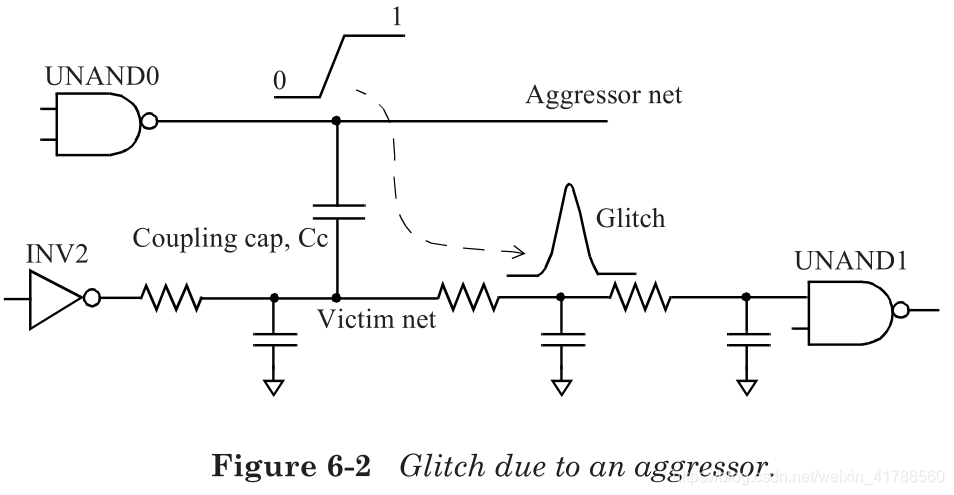

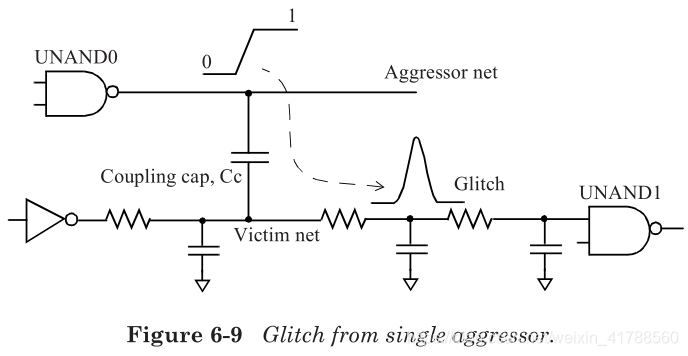

由于开关攻击者通过耦合电容传输的电荷,稳定的信号网络可能会出现毛刺(正或负)。图 6-2 说明了由上升的攻击者网络的串扰引起的正毛刺。两个网络之间的耦合电容被描述为一个集总电容 Cc 而不是分布式耦合,这是为了简化下面的说明,而又不失一般性。在提取的网表的典型表示中,耦合电容可能分布在多个段上,如前面第 6.1 节中所见。

在此示例中,NAND2 单元 UNAND0 对其输出网络(标记为 Aggressor)进行切换和充电。一些电荷也通过耦合电容 Cc 转移到受害网络并导致正毛刺。转移的电荷量与攻击者和受害网络之间的耦合电容 Cc 直接相关。在受害网络的接地电容上传输的电荷会导致该网络出现故障。由于传输的电荷通过驱动单元 INV2 的下拉阶段耗散,因此受害网络上的稳定值(在这种情况下为 0 或低)恢复。

引起的毛刺的大小取决于多种因素。其中一些因素是:

- 攻击者网络和受害者之间的耦合电容:耦合电容越大,毛刺的幅度越大。

- 攻击者网络的转换(slew):攻击者网络的转换速度越快,毛刺的幅度就越大。通常,更快的转换是因为驱动攻击者网络的单元具有更高的输出驱动强度。

- 受害网络接地电容:受害网络上的接地电容越小,毛刺的幅度越大。

- 受害网络驱动强度:驱动受害网络的单元的输出驱动强度越小,毛刺的幅度越大。

总体而言,虽然受害网络上的稳定值得到恢复,但毛刺会由于下述原因影响电路的功能。

- 毛刺幅度可能大到足以被扇出单元视为不同的逻辑值(例如,逻辑 0 处的受害者可能表现为扇出单元的逻辑 1)。这对于顺序单元(触发器、锁存器)或存储器尤其重要,其中时钟故障或异步设置/复位可能对设计的功能造成灾难性影响。类似地,锁存器输入端数据信号上的毛刺会导致不正确的数据被锁存,如果在输入数据时出现毛刺,这也可能是灾难性的。

- 即使受害网络不驱动顺序单元,宽毛刺也可能通过受害网络的扇出传播并到达顺序单元输入,对设计造成灾难性后果。

毛刺类型(Types of Glitches)

毛刺具有许多不同种类:

上升和下降毛刺(Rise and Fall Glitches)

前面小节中的讨论说明了受害者网络上的上升毛刺(Rise Glitch),该受害者网络一直稳定在低电平。类似的情况是在稳定的高电平信号上出现负毛刺,电平下降切换的攻击者网络会在稳定的高电平信号上引起下降毛刺(Fall Glitch)。

过冲和欠冲毛刺(Overshoot and Undershoot Glitches)

当一个上升的攻击者与一个稳定高电平的受害者网络结合时会发生什么?仍然存在使受害网络电压高于其稳定高值的毛刺。这种毛刺称为过冲毛刺(overshoot glitch)。类似地,当耦合到稳定的低电平受害网络时,下降的攻击者会导致受害网络上出现欠冲毛刺(Undershoot Glitches)。

图 6-3 说明了由串扰引起的所有四种毛刺情况。

如上一小节所述,毛刺由耦合电容、攻击者转换和受害者网络的驱动强度决定。毛刺计算基于开关攻击者注入的电流量、受害者网络的RC互连以及驱动受害者网络的单元的输出阻抗。详细的毛刺计算基于库模型;用于计算的相关噪声模型是第3章中描述的标准单元库模型的一部分。第3.7节中的输出 dc_current模型与单元的输出阻抗相关。

毛刺阈值和传播(Glitch Thresholds and Propagation)

如何确定网络上的毛刺是否可以通过扇出单元传播?正如前面的小节所讨论的,由开关干扰源耦合引起的毛刺可以通过扇出单元传播,具体取决于扇出单元和毛刺属性,例如毛刺高度和毛刺宽度。这种分析可以基于直流或交流噪声阈值。 DC 噪声分析仅检查毛刺幅度并且是保守的,而 AC 噪声分析检查其他属性,例如毛刺宽度和扇出单元输出负载。下面描述了在毛刺的 DC 和 AC 分析中使用的各种阈值指标。

直流阈值(DC Thresholds)

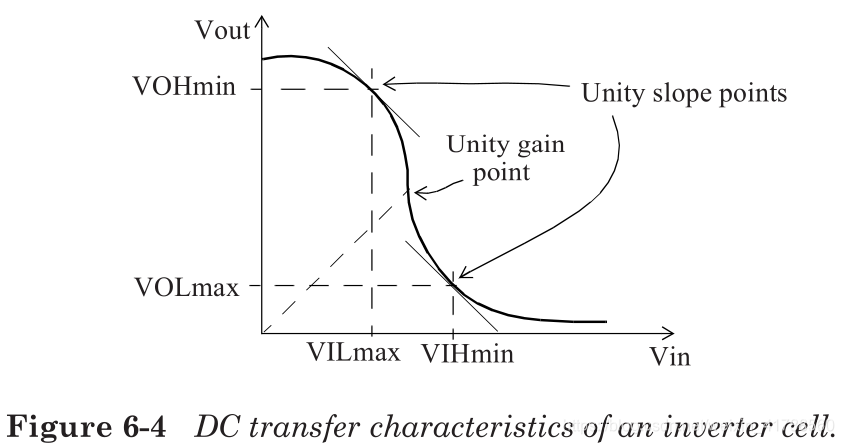

DC 噪声容限(noise margin)是用于检查毛刺幅度的检查,指的是确保正确的逻辑功能同时,单元输入的 DC 噪声限制。例如,只要输入保持在单元的 VIL 最大值以下,反相器单元的输出就可以是高的(即,保持在 VOH 的最小值以上)。类似地,只要输入保持在 VIH 最小值以上,反相器单元的输出就可以是低的(即保持在 VOL 最大值以下)。这些限制是根据单元的直流传输特性获得的,并且可以填充在单元库中。

VOH 是被视为逻辑 1 或高的输出电压范围。 VIL 是被视为逻辑零或低的输入电压范围。 VIH 是被视为逻辑 1 的输入电压范围。 VOL 是被视为逻辑零的输出电压范围。图 6-4 给出了逆变器单元输入-输出直流传输特性的示例。

VILmax 和 VIHmin 限制也称为 DC 裕度限制。基于 VIH 和 VIL 的直流裕度是稳态噪声限值。因此,这些可以用作确定毛刺是否会通过扇出单元传播的过滤器。 DC 噪声容限限制适用于单元的每个输入引脚。通常,对于rise_glitch(输入低)和fall_glitch(输入高),DC 裕度限制是分开的。 DC 裕度的模型可以指定为单元库描述的一部分。无论毛刺的宽度如何,低于 DC 裕度限制的毛刺(例如,低于扇出引脚 VILmax 的上升毛刺)都无法通过扇出传播。因此,保守的毛刺分析检查峰值电压电平(对于所有毛刺)是否满足扇出单元的 VIL 和 VIH 电平。只要所有网络满足扇出单元的 VIL 和 VIH 水平,尽管存在任何毛刺,就可以得出结论,毛刺对设计的功能没有影响(因为毛刺不会导致输出改变)。

图 6-5 显示了直流裕度限制的示例。对于设计中的所有网络,DC 噪声容限也可以固定为相同的限制。可以设置最大的可容忍噪声(或毛刺)幅度,高于该幅度的噪声可以通过单元传播到输出引脚。通常,此检查可确保毛刺电平小于 VILmax 且大于 VIHmin。高度通常表示为电源的百分比。因此,如果 DC 噪声容限设置为 30%,则表明任何大于电压摆幅 30% 的毛刺高度都被识别为潜在毛刺,它可以通过单元传播并可能影响设计的功能。

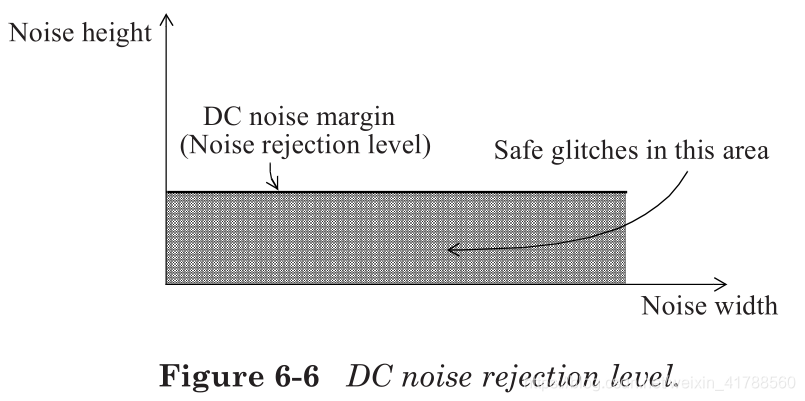

并非所有幅度大于直流噪声容限的毛刺都能改变单元的输出。在确定毛刺是否会传播到输出时,毛刺的宽度也是一个重要的考虑因素。单元输入处的窄毛刺通常不会对单元输出造成任何影响。然而,无论信号噪声宽度如何,直流噪声容限仅使用恒定的最坏情况值。参见图 6-6。这提供了噪声抑制水平,它是对单元噪声容限的非常保守的估计。

交流阈值(AC Thresholds)

如上小节所述,毛刺分析的 DC 裕度限制是保守的,因为这些限制是在最坏情况下分析设计的。 DC 裕量限制验证即使毛刺任意宽,也不会影响设计的正常运行。

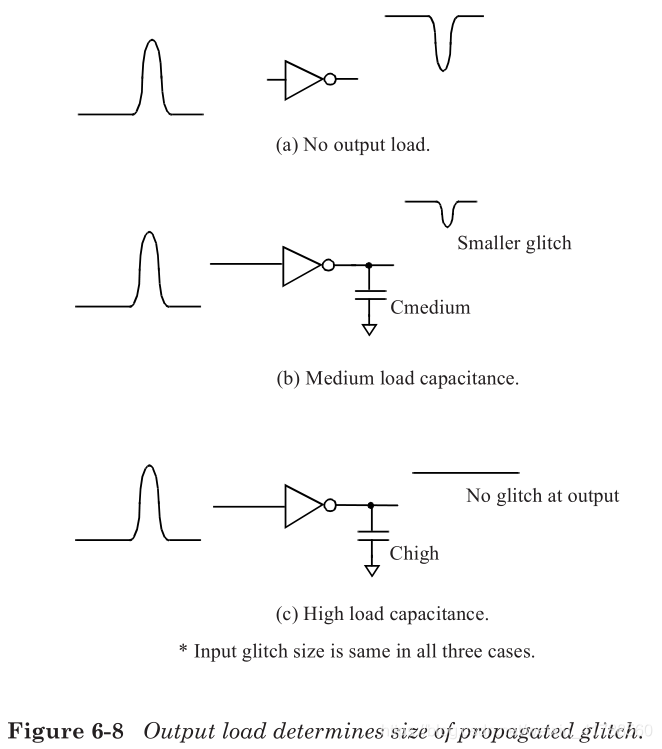

在大多数情况下,设计可能无法通过保守的 DC 噪声分析限制。因此,必须验证毛刺对毛刺宽度和单元输出负载的影响。通常,如果毛刺很窄或者如果扇出单元具有大的输出电容,则毛刺不会影响正常的功能操作。毛刺宽度和输出电容的影响都可以用扇出单元的惯性来解释。通常,单级单元将停止比通过单元的延迟窄得多的任何输入毛刺。这是因为对于窄毛刺,毛刺在扇出单元可以响应之前就结束了。因此,非常窄的毛刺不会对电池产生任何影响。由于输出负载增加了通过单元的延迟,因此增加输出负载具有将输入端毛刺的影响降至最低的效果,尽管它具有增加单元延迟的不利影响。

AC 噪声抑制如图 6-7 所示(对于固定输出电容)。深色阴影区域代表良好或可接受的毛刺,因为这些毛刺太窄或太短,或两者兼而有之,因此对单元的功能行为没有影响。浅阴影区域表示不良或不可接受的毛刺,因为这些毛刺太宽或太高,或既宽又高,因此在单元输入端的这种毛刺会影响单元的输出。在毛刺较宽的极限情况下,毛刺阈值对应于DC噪声裕量,如图6-7所示。

对于给定的单元,增加输出负载会增加噪声容限,因为它会增加惯性延迟和可以通过单元的毛刺宽度。下面通过一个例子来说明这种现象。图 6-8(a) 显示了一个无负载的逆变器单元,其输入端有一个正毛刺。输入毛刺高于单元的直流裕度,并导致逆变器输出出现毛刺。图 6-8(b) 显示了在其输出端带有一些负载的相同逆变器单元。输入端相同的输入毛刺会导致输出上的毛刺小得多。如果逆变器单元的输出负载更高,如图 6-8(c) 所示,则逆变器单元的输出没有任何毛刺。因此,增加输出端的负载会使单元更不受从输入端传播到输出端的噪声的影响。

如上所述,低于 AC 阈值(图 6-7 中的 AC 噪声抑制区域)的毛刺可以被忽略,或者可以认为扇出单元不受此类毛刺的影响。 AC 阈值(或抗扰度)区域取决于输出负载和毛刺宽度。如第3章中所述,抗扰度模型(noise immunity model)包括上述AC噪声抑制的影响,3.7节中介绍的propagated_noise模型除了对通过单元的传播进行建模外,还包括了AC噪声阈值的影响。

如果毛刺大于 AC 阈值会发生什么?在毛刺幅度超过 AC 阈值的情况下,单元输入处的毛刺会在单元输出处产生另一个毛刺。输出毛刺高度和宽度是输入毛刺宽度和高度以及输出负载的函数。此信息在单元库中进行了表征,其中包含输出毛刺幅度和宽度的详细表格或函数,作为输入引脚毛刺幅度、毛刺宽度和输出引脚负载的函数。毛刺传播由包含在库单元描述中的propagated_noise模型控制。propagated_noise(低和高)模型在第 3 章中详细描述。

基于以上内容,在扇出单元的输出处计算毛刺,并在扇出网络上进行相同的检查(以及毛刺传播到扇出),依此类推。

虽然我们在上面的讨论中使用了通用术语“毛刺”,但应注意,这分别适用于前一小节中提到的所有类型的毛刺:上升毛刺(由早期模型中的propagated_noise_high或noise_immunity_high建模),下降毛刺(由早期模型中的propagated_noise_low或noise_immunity_low建模),过冲毛刺(由noise_immunity_above_high建模)和欠冲毛刺(由noise_immunity_below_low建模)。

总之,单元的不同输入对毛刺阈值有不同的限制,毛刺阈值是毛刺宽度和输出电容的函数。这些限制对于输入高(低转换毛刺)和输入低(高转换毛刺)是分开的。噪声分析会检查毛刺的峰值和宽度,并分析它是否可以被忽略或它是否可以传播到扇出。

多个干扰源的噪声累积(Noise Accumulation with Multiple Aggressors)

图 6-9 描述了由于单个攻击者网络切换和在受害网络上引入串扰毛刺引起的耦合。一般而言,受害网络可以电容耦合到许多网络。当多个网络同时切换时,由于有多个攻击者,串扰耦合噪声对受害者的影响更加复杂。

由于多个攻击者引起的耦合的大多数分析都会添加由于每个攻击者引起的毛刺效应,并计算对受害者的累积影响。这可能看起来很保守,但它确实表明了受害者最坏的情况。另一种方法是使用 RMS(均方根)方法。使用 RMS 选项时,受害设备上的毛刺幅度是通过取个别攻击者引起的毛刺的均方根来计算的。

干扰源时序相关性(Aggressor Timing Correlation)

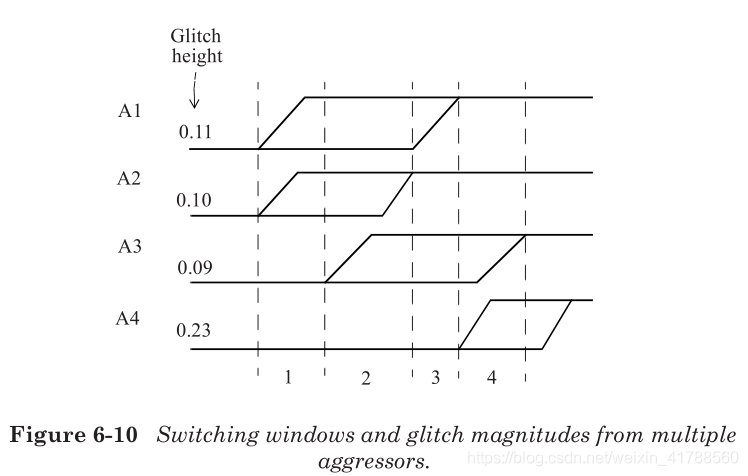

对于由多个干扰源引起的串扰毛刺,分析必须包括干扰源网络的时序相关性,并确定多个干扰源是否可以同时切换。 STA 从攻击者网络的时序窗口中获取此信息。在时序分析过程中,得到网络最早和最晚的切换时间。这些时间代表网络可以在一个时钟周期内切换的时序窗口。切换窗口(上升和下降)提供有关攻击者网络是否可以一起切换的必要信息。

根据多个干扰源是否可以同时切换,将单个干扰源造成的毛刺组合起来用于受害网络。作为第一步,毛刺分析为每个潜在干扰源分别计算四种类型的毛刺(上升、下降、欠冲和过冲)。下一步结合来自各个干扰源的故障贡献。多个干扰源可以针对每种类型的毛刺单独组合。例如,考虑耦合到攻击者网络 A1、A2、A3 和 A4 的受害者网络 V。在分析过程中,A1、A2 和 A4 可能会导致上升和过冲毛刺,而只有 A2 和 A3 会导致欠冲和下降毛刺。

考虑另一个示例,其中当攻击者网络转换时,四个攻击者网络会导致上升的毛刺。图 6-10 显示了由每个攻击者网络引起的时序窗口和毛刺幅度。根据时序窗口,毛刺分析确定导致最大毛刺的干扰源切换的最坏可能组合。在这个例子中,切换窗口区域被分为四个 bin - 每个 bin 显示可能的干扰源切换。图 6-10 还描述了来自每个干扰源的毛刺贡献。 Bin 1 具有 A1 和 A2 切换,这可能导致 0.21 (= 0.11+ 0.10) 的毛刺幅度。 Bin 2 具有 A1、A2 和 A3 切换,这会导致毛刺幅度为 0.30 (= 0.11+ 0.10+ 0.09)。 Bin 3 具有 A1 和 A3 切换,这会导致毛刺幅度为 0.20 (= 0.11 +0.09)。 Bin 4 具有 A3 和 A4 切换,这会导致毛刺幅度为 0.32 (= 0.09+ 0.23)。

因此,bin 4 具有 0.32 的最坏可能的毛刺幅度。请注意,不使用时序窗口的分析将预测组合毛刺幅度为 0.53 (= 0.11+ 0.10+ 0.09 +0.23),这可能过于悲观。

干扰源功能相关性(Aggressor Functional Correlation)

对于多个干扰源,通过考虑网络可能切换的切换窗口,使用时序窗口减少了分析中的悲观情绪。此外,另一个需要考虑的因素是各种信号之间的功能相关性。例如,scan(在DFT test mode) 控制信号仅在扫描模式期间切换,并且在设计的功能或任务模式期间稳定。因此,在功能模式期间,扫描控制信号不会对其他信号造成毛刺。扫描控制信号只能是扫描模式期间的干扰源。在某些情况下,测试时钟和功能时钟是相互排斥的,因此测试时钟仅在测试期间当功能时钟关闭时才有效。在这些设计中,由测试时钟控制的逻辑和由功能时钟控制的逻辑创建了两组不相交的干扰源。在这种情况下,测试时钟控制的干扰源不能与功能时钟控制的其他干扰源结合进行最坏情况噪声计算。功能相关的另一个例子是两个干扰源,它们是彼此的补充(逻辑相反)。在这种情况下,信号及其补码不能在相同方向上切换以计算串扰噪声。

图 6-11 显示了网络 N1 与其他三个网络 N2、N3 和 N4 耦合的示例。在功能关联中,需要考虑网络的功能。假设网络 N4 是一个常数(例如,模式设置网络),因此不能成为网络 N1 上的干扰源,尽管它是耦合的。假设 N2 是一个网络,它是调试总线的一部分,但在功能模式下处于稳定状态。因此,网络 N2 不能成为网络 N1 的干扰源。假设网络 N3 携带功能数据,只有网络 N3 可以被视为网络 N1 的潜在干扰源。

串扰延迟分析(Crosstalk Delay Analysis)

基础知识(Basics)

纳米设计中典型网络的电容提取由许多相邻导体的贡献组成。其中一些是接地电容,而其他许多来自作为其他信号网络一部分的走线。接地电容和信号间电容如图 6-1 所示。在基本延迟计算期间,所有这些电容都被视为网络总电容的一部分(不考虑任何串扰)。当相邻网络稳定(或未切换)时,信号间电容可被视为接地。当相邻网络切换时,通过耦合电容的充电电流会影响网络的时序。根据攻击者网络切换的方向,从网络上看到的等效电容可以更大或更小。这在下面的一个简单示例中进行了解释。

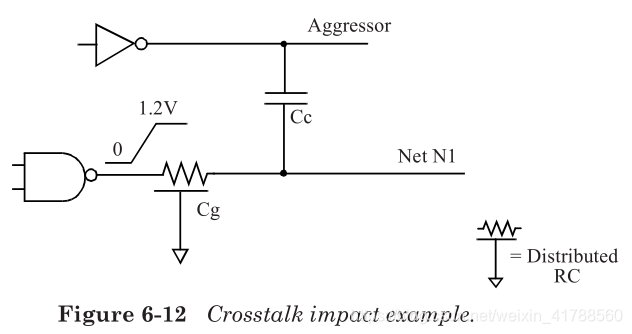

图 6-12 显示了网络 N1,它有一个到相邻网络(标记为 Aggressor)的耦合电容 Cc 和一个到地的电容 Cg。此示例假设网络 N1 在输出端具有上升过渡,并根据攻击者网络是否同时切换来考虑不同的场景。

如下文所述,驱动单元在各种情况下所需的电容性电荷可能不同。

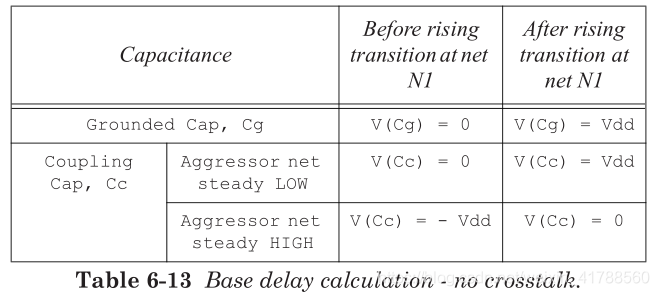

- 攻击者网络处于稳定状态:在这种情况下,网络N1的驱动单元将提供电荷使Cg和Cc充电至Vdd。因此,该网络的驱动单元提供的总电荷为(Cg + Cc)* Vdd。这种情况可以进行基本的延迟计算,因为在这种情况下未考虑来自攻击者网络的串扰。表6-13中为此情况下在网络N1电平切换前后Cg和Cc中的电荷量:

- 攻击者网络朝同方向切换电平: 在这种情况下,往同方向电平切换的攻击者网络可以起辅助驱动单元的作用。如果攻击者网络同时以相同的转换slew(相同的transition time)进行电平切换,则驱动单元提供的总电荷仅为(Cg * Vdd )。如果攻击者网络的转换比N1网络转换更快,则所需的实际电荷可能甚至小于(Cg * Vdd),因为攻击者网络也可以为Cg提供充电电流。因此,在攻击者朝相同方向切换电平时,来自驱动单元的所需电荷会小于表6-13中描述的攻击者处于稳定状态时的所需电荷。因此,当攻击者网络朝相同方向切换电平时会导致网络N1切换电平的延迟更短, 延迟的减少被标记为负串扰延迟(negative crosstalk delay)。这种情况请参见表6-14,通常会在进行最小路径分析时考虑此情况。

- 攻击者网络朝相反方向切换电平:在这种情况下,耦合电容需要从-Vdd充电到Vdd。因此在电平切换前后,耦合电容上的电荷变化量为(2 * Cc * Vdd),网络N1的驱动单元以及攻击者网络均需要提供额外的电荷。这种情况会导致网络N1切换电平的延迟更大,延迟的增加被标记为正串扰延迟(positive crosstalk delay)。这种情况请参阅表6-15,通常会在进行最大路径分析时考虑此情况。

上面的例子说明了 Cc 在各种情况下的充电以及它如何影响交换网络的延迟(标记为 N1)。该示例仅考虑网络 N1 处的上升过渡,但类似的分析也适用于下降过渡。

正负串扰(Positive and Negative Crosstalk)

基本延迟计算(没有任何串扰)假设驱动单元为网络总电容 Ctotal (= Cground +Cc) 的轨到轨(rail-to-rail)转换提供所有必要的电荷。如前一小节所述,当耦合(攻击者)网络和受害者网络在相反方向切换时,耦合电容 Cc 所需的电荷更大。在相反方向上的攻击者切换增加了受害网络的驱动单元所需的电荷量,并增加了受害网络的驱动单元和互连的延迟。

类似地,当耦合(攻击者)网络和受害者网络在同一方向切换时,Cc 上的电荷在受害者和攻击者转换之前和之后保持不变。这减少了受害网络的驱动单元所需的电荷。减少了驱动单元和受害网络互连的延迟。

如上所述,受害者和攻击者的并发切换会影响受害者转换的时间。根据干扰源的切换方向,串扰延迟效应可以是正的(减缓受害转换)或负的(加速受害转换)。

图 6-16 显示了正串扰延迟效应的示例。当受害网络发生下降过渡时,攻击者网络正在上升。相反方向的攻击者网络切换增加了受害网络的延迟。正串扰会影响驱动单元和互连——这两者的延迟都会增加。

图6-17显示了串扰延迟为负的情况。攻击者网络与受害者网络同时上升,攻击者网络与受害者网络朝相同方向的电平切换可减少受害者网络的延迟。如前所述,负串扰(negative crosstalk)会影响驱动单元和互连线的时序,两者的延迟都会减小。

注意,最差的正串扰延迟和最差的负串扰延迟会分别针对上升和下降延迟进行计算。一般来说,由于串扰而导致的最大上升时间、最小上升时间、最大下降时间、最大下降时间延迟的干扰源是不同的,这将在下面的小节中进行介绍。

多个干扰源的累积(Accumulation with Multiple Aggressors)

具有多个干扰源的串扰延迟分析涉及对每个干扰源的串扰造成的影响进行累加。这类似于第 6.2 节中描述的串扰毛刺分析。当多个网络同时切换时,由于多个攻击者,对受害者的串扰延迟效应会变得更加复杂。

由于多个干扰源引起的耦合的大多数分析都会添加每个攻击者的增量贡献并计算对受害者的累积影响。这可能看起来很保守,但它确实表明受害设备上的最坏情况串扰延迟。

与用于串扰毛刺分析的多个干扰源的分析类似,也可以使用均方根 (RMS) 来添加贡献,这比单个贡献的直和更不悲观。

攻击者-受害者时间相关性(Aggressor Victim Timing Correlation)

串扰延迟分析的时序相关处理在概念上类似于第 6.2 节中描述的串扰毛刺分析的时序相关。串扰会影响受害者的延迟,前提是攻击者可以与受害者同时切换。这是使用攻击者和受害者的时序窗口确定的。如第 6.2 节所述,时序窗口表示网络可以在一个时钟周期内切换的最早和最晚切换时间。如果攻击者和受害者的时序窗口重叠,则计算串扰对延迟的影响。对于多个攻击者,多个攻击者的时序窗口也进行了类似的分析。计算各种时序仓中的可能影响,并考虑串扰延迟影响最严重的时序仓进行延迟分析。

考虑下面的示例,其中三个攻击者网络可以影响受害者网络的时间。攻击者网络 (A1, A2, A3) 电容耦合到受害者网络 (V) 并且它们的时序窗口与受害者网络重叠。图 6-18 显示了时序窗口和每个干扰源可能造成的串扰延迟影响。基于时序窗口,串扰延迟分析确定引起最大串扰延迟影响的干扰源切换的最坏可能组合。在这个例子中,时间窗口重叠区域被分成三个 bin - 每个 bin 显示可能的攻击者切换。 Bin 1 具有 A1 和 A2 切换,这会导致串扰延迟影响为 0.26 (= 0.12 +0.14)。 Bin 2 具有 A1 切换,这会导致 0.14 的串扰延迟影响。 Bin 3 具有 A3 切换,可导致 0.23 的串扰延迟影响。因此,bin 1 具有 0.26 的最坏可能的串扰延迟影响。

如前所述,串扰延迟分析将分别计算四种类型的串扰延迟。串扰延迟的四种类型是:正上升延迟(上升沿提前到达)、负上升延迟(上升沿滞后到达)、正下降延迟和负下降延迟。通常,在这四种情况下,网络可以具有不同的攻击者组合。例如,受害者网络具有攻击者网络A1、A2、A3和A4。在串扰延迟分析过程中,A1、A2、A4可能对正上升和负下降延迟有影响,而A2和A3对负上升和正下降延迟有影响。

攻击者-受害者功能相关性(Aggressor Victim Functional Correlation)

除了时序窗口,串扰延迟计算还可以考虑各种信号之间的功能相关性。例如,扫描控制信号仅在扫描模式期间切换并且在设计的功能或任务模式期间稳定。因此,扫描控制信号在功能模式期间不能成为干扰源。在扫描模式期间,扫描控制信号只能是干扰源,在这种情况下,这些信号不能与其他功能信号组合以进行最坏情况噪声计算。

功能相关的另一个例子是两个干扰源互为补充的场景。在这种情况下,信号及其补码永远不能在相同方向上切换以计算串扰噪声。当可用时,可以利用这种类型的函数相关信息,从而通过确保只有实际可以一起切换的信号作为干扰源被包括在内,从而使串扰分析结果不悲观。

使用串扰延迟进行时序验证(Timing Verification Using Crosstalk Delay)

需要为设计中的每个单元和互连线计算以下四种类型的串扰延迟影响:

- 正上升延迟(Positive rise delay):上升沿提前到达

- 负上升延迟(Negative rise delay):上升沿滞后到达

- 正下降延迟(Positive fall delay):下降沿提前到达

- 负下降延迟(Negative fall delay):下降沿滞后到达

然后在时序分析期间利用串扰延迟贡献来验证最大和最小路径(setup and hold checks)。启动和捕获触发器的时钟路径处理方式不同。本节描述了用于建立和保持检查的数据路径和时钟路径分析的详细信息。

6.4.1建立时间分析(Setup Analysis)

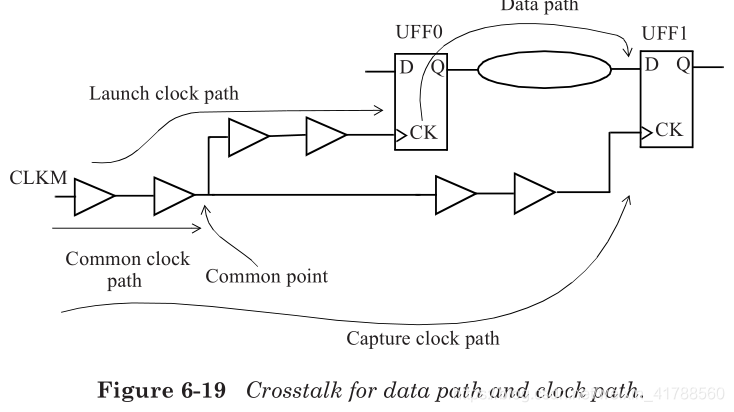

具有串扰分析功能的 STA 使用数据路径和时钟路径的最坏情况串扰延迟来验证设计。考虑图 6-19 中所示的逻辑,其中数据路径和时钟路径上的各种网络可能会发生串扰。建立时间检查的最坏情况是启动时钟路径(launch clock path)和数据路径都具有正串扰,而捕获时钟路径(capture clock path)具有负串扰。发射时钟路径和数据路径上的正串扰贡献延迟了数据到达捕获触发器。此外,捕获时钟路径上的负串扰导致捕获触发器提前计时。

基于以上描述,建立时间(或最大路径)分析假设:

- 发起时钟路径出现正串扰延迟,因此发起数据较迟。

- 数据路径出现正串扰延迟,因此数据到达目的地需要更长的时间。

- 捕获时钟路径出现负串扰延迟,因此数据被捕获触发器提早捕获。

由于建立时间检查的启动和捕获时钟沿不同(通常相隔一个时钟周期),公共时钟路径(图 6-19)可能对启动和捕获时钟沿有不同的串扰贡献。

6.4.2保持时间分析(Hold Analysis)

STA 的最坏情况保持时间(或最小路径)分析类似于上一小节中描述的最坏情况设置分析。根据图 6-19 中所示的逻辑,当启动时钟路径和数据路径都具有负串扰并且捕获时钟路径具有正串扰时,会发生保持时间检查的最坏情况。发射时钟路径和数据路径上的负串扰贡献导致数据提前到达捕获触发器。此外,捕获时钟路径上的正串扰导致捕获触发器的时钟延迟。

与时钟路径公共部分上的串扰相关的保持时间和建立时间分析之间存在一个重要区别。对于保持时间分析,启动和捕获时钟边沿通常是相同的边沿。通过公共时钟部分的时钟沿不能对启动时钟路径和捕获时钟路径具有不同的串扰贡献。因此,最坏情况保持时间分析消除了公共时钟路径中的串扰影响。

因此,具有串扰的STA最差情况保持时间(或最小路径)分析将假定:

- 发起时钟(不包括公共时钟路径部分)的串扰延迟影响为负,因此可以较早地发起数据;

- 数据路径的串扰延迟影响为负,因此数据会较早到达目的地;

- 捕获时钟(不包括公共时钟路径部分)的串扰延迟影响为正,因此捕获触发器会较迟地捕获数据

如上所述,保持时间分析不考虑对时钟树公共部分的串扰影响。仅针对时钟树的非公共部分计算启动时钟的正串扰贡献和捕获时钟的负串扰贡献。在用于保持分析的 STA 报告中,公共时钟路径可能会显示启动时钟路径和捕获时钟路径的不同串扰贡献。然而,来自公共时钟路径的串扰贡献作为单独的行项目被移除,标记为公共路径悲观消除。 STA 报告中常见路径悲观消除的示例在第 10.1 节中提供。

如前一小节所述,建立时间分析涉及时钟的两个不同边沿,它们可能会在时序上受到不同的影响。因此,在建立时间分析期间,对启动和捕获时钟路径都考虑了公共路径串扰贡献。

时钟信号至关重要,因为时钟树上的任何串扰都会直接转化为时钟抖动并影响设计的性能。因此,应特别考虑减少时钟信号上的串扰。一种常见的噪声避免方法是时钟树的屏蔽——这将在第 6.6 节中详细讨论。

计算复杂性(Computational Complexity)

大型纳米设计通常过于复杂,无法在合理的周转时间内分析每个耦合电容。典型网络的寄生提取包含与许多相邻信号的耦合电容。大型设计通常需要为寄生提取和串扰延迟和毛刺分析进行适当的设置。选择这些设置是为了提供可接受的分析精度,同时确保 CPU 要求仍然可行。本节介绍一些可用于分析大型纳米设计的技术。

分层设计和分析(Hierarchical Design and Analysis)

第 4.5 节介绍了验证大型设计的分层方法。类似的方法也适用于降低提取和分析的复杂性。

对于大型设计,在一次运行中获得寄生提取通常是不切实际的。可以单独提取每个分层块的寄生参数。这反过来又要求在设计实现中使用分层设计方法。这意味着分层块内的信号和块外的信号之间没有耦合。这可以通过在块上不布线或通过在块上添加屏蔽层来实现。此外,信号网络不应靠近模块边界布线,靠近模块边界布线的任何网络都应屏蔽。这避免了与来自其他块的网络的任何耦合。

耦合电容滤波(Filtering of Coupling Capacitances)

即使对于中等大小的模块,寄生效应通常也会包括大量非常小的耦合电容。可以在提取或分析过程中过滤小耦合电容。

这样的过滤是基于以下原则的:

- 较小的值:在串扰或噪声分析中,可以忽略非常小的耦合电容,例如低于1fF。在提取过程中,数值较小的耦合电容可以视为接地电容。

- 耦合比:耦合对受害者网络的影响是基于耦合电容相对于受害者网络总电容的相对值。具有较小耦合比(例如低于0.001)的攻击者网络可以从串扰延迟分析或串扰毛刺分析中排除。

- 合并小型干扰源:可以将影响很小的多个干扰源映射为一个较大的虚拟干扰源。这可能有点悲观,但可以简化分析。可以通过切换干扰源的子集来缓解一些悲观度,干扰源的确切子集可以通过统计方法来确定。

噪声避免技术(Noise Avoidance Techniques)

前面的部分描述了串扰效应的影响和分析。在本节中,我们将介绍一些可在物理设计阶段使用的噪声避免技术。

- 屏蔽(Shielding):此方法要求将屏蔽线放置在关键信号的任一侧。屏蔽连接到电源或接地导轨。关键信号的屏蔽确保关键信号没有主动干扰源,因为同一金属层中最近的邻居是固定电位的屏蔽走线。虽然不同金属层中的路径可能存在一些耦合,但大多数耦合电容是由于同一层中的电容耦合。由于不同金属层(上方和下方)通常会正交走线,这样跨层的电容耦合会最小化。因此,将屏蔽线放置在同一金属层中可确保关键信号的耦合最小。在由于布线拥塞而无法使用接地或电源轨进行屏蔽的情况下,具有低开关活动(例如在功能模式期间固定的扫描控制)的信号可以作为关键信号的直接邻居进行布线。这些屏蔽方法可确保不会因相邻设备的电容耦合而产生串扰。

- 线间距(Wire spacing):这减少了与相邻网络的耦合。

- 快速转换率(Fast slew rate):网络上的快速转换率意味着网络不易受串扰影响,并且本质上不受串扰效应的影响。

- 保持良好的稳定电源(Maintain good stable supply):这对于减少由于电源变化引起的抖动而不是串扰很重要。由于电源上的噪声,时钟信号上可能会引入大量噪声。应添加足够的去耦电容以将电源噪声降至最低。

- 保护环(Guard ring):基板中的保护环(或双保护环)有助于保护关键模拟电路免受数字噪声的影响。

- 深 n 阱(Deep n-well):这与上述类似,因为模拟部分具有深 n 阱有助于防止噪声耦合到数字部分。

- 隔离块(Isolating a block):在分层设计流程中,可以将布线晕圈(halos)添加到块的边界;此外,还可以将隔离缓冲器(isolation buffers)添加到块的每个IO中。

配置 STA 环境(Configuring the STA Environment)

第 7 章是后续章节的先决条件。它描述了如何配置时序分析环境。描述了指定时钟、IO 特性、伪路径和多周期路径的方法。

正确约束的说明对于分析STA结果非常重要。应准确指定设计环境,以便STA分析能够识别设计中的所有时序问题。STA的准备包括设置时钟、指定IO定时特性以及指定伪路径和多周期路径。在继续下一章关于时间验证之前,彻底理解本章非常重要。

什么是STA环境?(What is the STA Environment?)

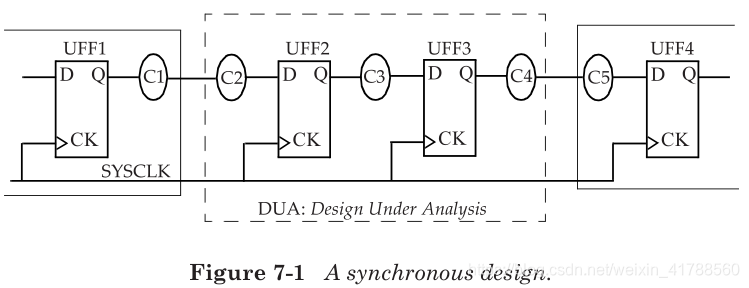

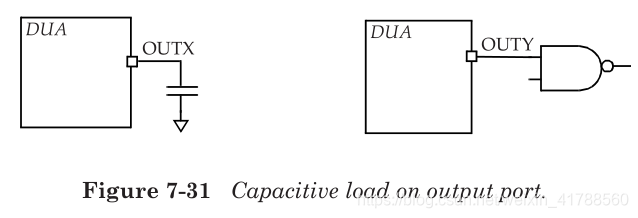

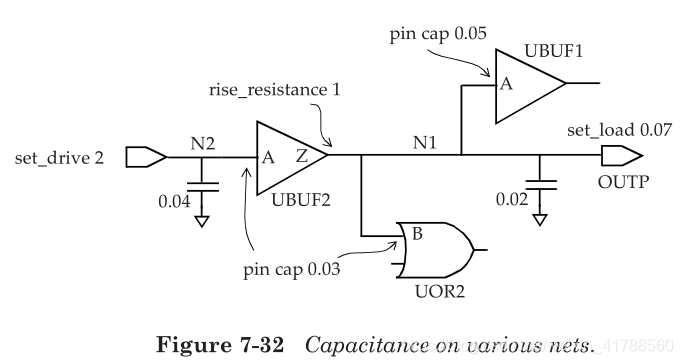

大多数数字设计都是同步的,从上一个时钟周期计算的数据锁存在活动时钟边缘的触发器中。考虑图7-1所示的典型同步设计,假设分析设计(DUA)与其他同步设计相互作用。这意味着DUA从时钟触发器接收数据,并将数据输出到DUA外部的另一个时钟触发器。

要在此设计上执行STA,需要指定触发器的时钟,以及通向设计的所有路径和退出设计的所有路径的时序约束。

图7-1中的示例假设只有一个时钟,C1、C2、C3、C4和C5表示组合块。组合块C1和C5不在所分析的设计范围内。

在典型设计中,从一个时钟域到另一个时钟域可以有多个时钟,具有多条路径。以下各节介绍如何在此类场景中指定环境。

指定时钟(Specifying Clocks)

要定义时钟,我们需要提供以下信息:

- 时钟源(Clock source):它可以是设计的端口,也可以是设计内部单元的引脚(通常是时钟生成逻辑的一部分)。

- 周期(Period):时钟的周期。

- 占空比(Duty cycle):高电平持续时间(正相位)和低电平持续时间(负相位)。

- 边沿时间(Edge times):上升沿和下降沿的时刻。

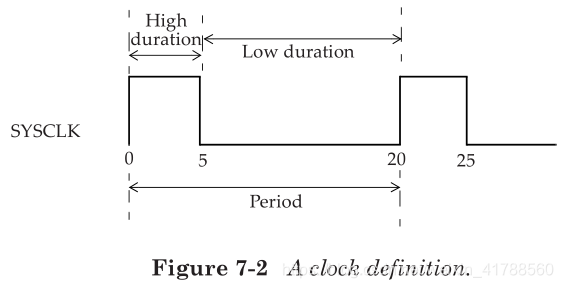

图7-2显示了基本定义。通过定义时钟,所有内部时序路径(所有触发器到触发器路径)都受到约束;这意味着所有内部路径都可以仅使用时钟规格进行分析。时钟规范规定触发器到触发器的路径必须占用一个周期。我们将在后面描述如何放宽这一要求(一个周期时间)。

以下是一个基本的时钟约束规范:

1 | create_clock \ |

时钟的名称为SYSCLK,在端口SCLK处定义。SYSCLK的周期指定为20个单位-如果未指定,则默认时间单位为纳秒(通常,时间单位指定为技术库的一部分。)波形中的第一个参数指定上升沿出现的时间,第二个参数指定下降沿出现的时间。

waveform选项中可以指定任意数量的边。但是,所有边缘必须在一个周期内。沿时间从时间零点后的第一个上升沿开始交替,然后是下降沿,然后是上升沿,依此类推。这意味着waveform列表中的所有时间值必须是单调递增的。

1 | -waveform {time_rise time_fall time_rise time_fall ...} |

此外,必须指定偶数条边。 waveform选项指定一个时钟周期内的波形,然后该时钟周期自身重复。

如果未指定waveform选项,默认值为:

1 | -waveform {0, period/2} |

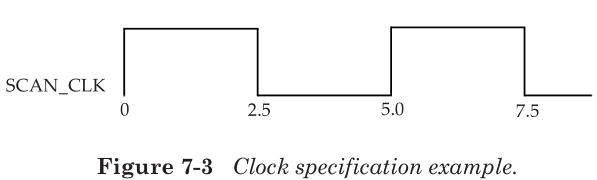

这里是一个没有波形规范的时钟规范示例(见图7-3)。

1 | create_clock -period 5 [get_ports SCAN_CLK] |

在此约束中,由于未指定-name选项,因此时钟的名称与端口的名称相同,即SCAN_CLK。

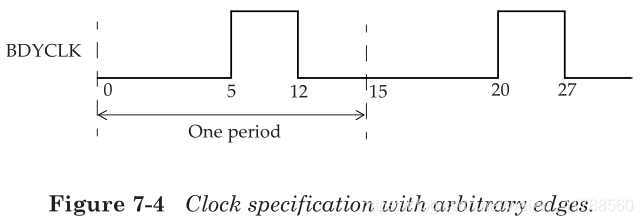

以下是时钟约束的另一个示例,其中波形的边沿在一个周期的中间位置(见图7-4)。

1 | create_clock -name BDYCLK -period 15 \ |

时钟的名称为BDYCLK,在端口GBLCLK处定义。实际上,保持时钟名称与端口名称相同是一个好主意。

这里有更多的时钟约束示例。

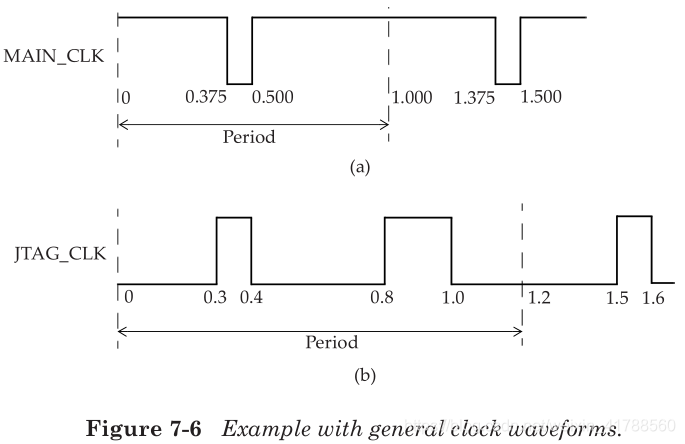

1 | # See Figure 7-5(a): |

1 | # See Figure 7-6(a): |

锁相环PLL(Phase-locked loop):在专用集成电路中常用来产生高频时钟 。

除上述属性外,还可以选择指定时钟源处的转换时间。在某些情况下,例如某些PLL模型的输出或输入端口,该工具无法自动计算过渡时间。在这种情况下,明确指定时钟源处的转换时间非常有用。这是使用set_clock_transition命令指定的。

1 | set_clock_transition -rise 0.1 [get_clocks CLK_CONFIG] |

这个约束仅适用于理想时钟,一旦构建了时钟树就将其忽略,因为此时将会使用时钟引脚上的实际过渡时间。如果在输入端口上定义了时钟,也可以使用set_input_transition命令(参见7.7节)来约束时钟的转换。

时钟不确定性(Clock Uncertainty)

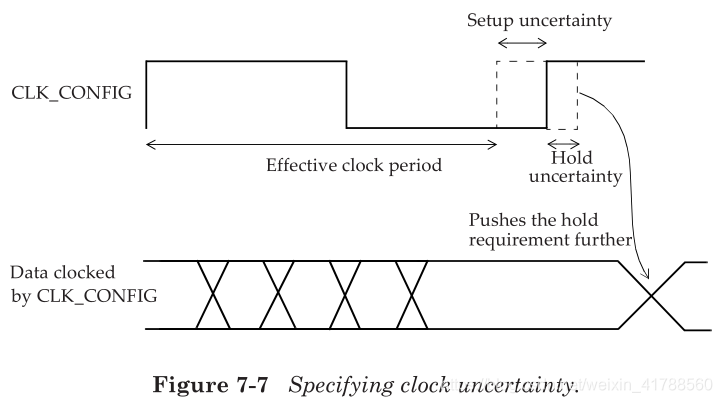

可以使用 set_clock_uncertainty 约束指定时钟周期的时序不确定性。不确定性可用于模拟可以减少有效时钟周期的各种因素。这些因素可以是时钟抖动和任何其他可能希望用于时序分析的悲观因素。

1 | set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG] |

注意,建立时间检查的时钟不确定度将减少可用的有效时钟周期,如图7-7所示。对于保持时间检查,时钟不确定度将用作需要满足的额外时序裕量。

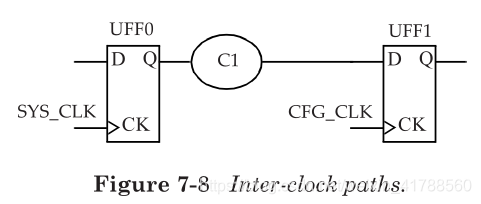

以下命令可用于指定跨时钟边界路径上的时钟不确定度,称为时钟间不确定度(inter-clock uncertainty)。

1 | set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK \ |

图 7-8 显示了两个不同时钟域 SYS_CLK 和 CFG_CLK 之间的路径。根据上述时钟间不确定性约束,100ps 用作建立时间检查的不确定性,50ps 用作保持时间检查的不确定性。

时钟延迟(Clock Latency)

可以使用set_clock_latency命令指定时钟的延迟。

1 | # Rise clock latency on MAIN_CLK is 1.8ns: |

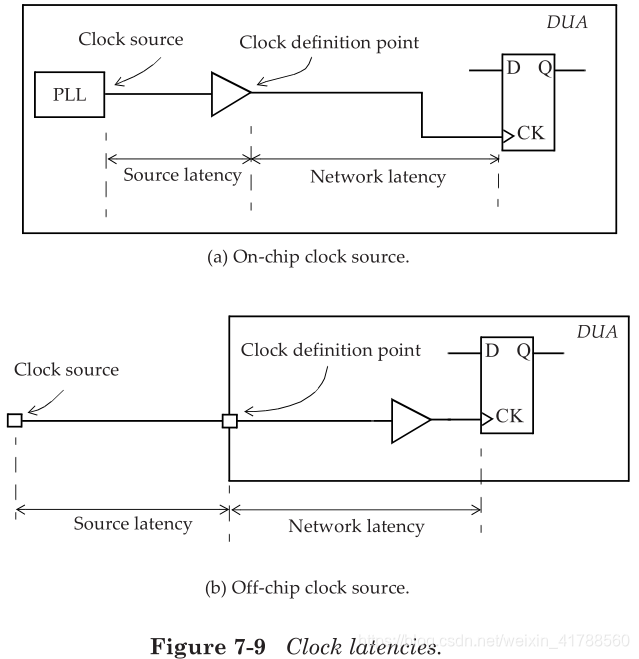

时钟延迟有两种类型:网络延迟(network latency)和源延迟(source latency)。网络延迟是从时钟定义点 (create_clock) 到触发器时钟引脚的延迟。源延迟,也称为插入延迟(insertion delay),是从时钟源到时钟定义点的延迟。源延迟可以代表片上或片外延迟。图 7-9 显示了这两种情况。触发器时钟引脚的总时钟延迟是源延迟和网络延迟的总和。

下面是一些指定源和网络延迟的示例命令。

1 | # Specify a network latency (no -source option) of 0.8ns for |

源延迟和网络延迟之间的一个重要区别是:一旦为设计建立了时钟树,就可以忽略网络延迟(假设指定了set_propagated_clock命令)。但是,即使在建立时钟树之后,源延迟也会保留。网络延迟是在进行时钟树综合(Clock Tree Synthesis)之前对时钟树延迟的估计值。在时钟树综合完成后,从时钟源到触发器时钟引脚的总时钟延迟是源延迟加上时钟树从时钟定义点到触发器的实际延迟。

生成时钟在下一节中描述,虚拟时钟在 7.9 节中描述。

生成时钟(Generated Clocks)

生成时钟是从主时钟派生的时钟。主时钟是使用 create_clock 命令定义的时钟。

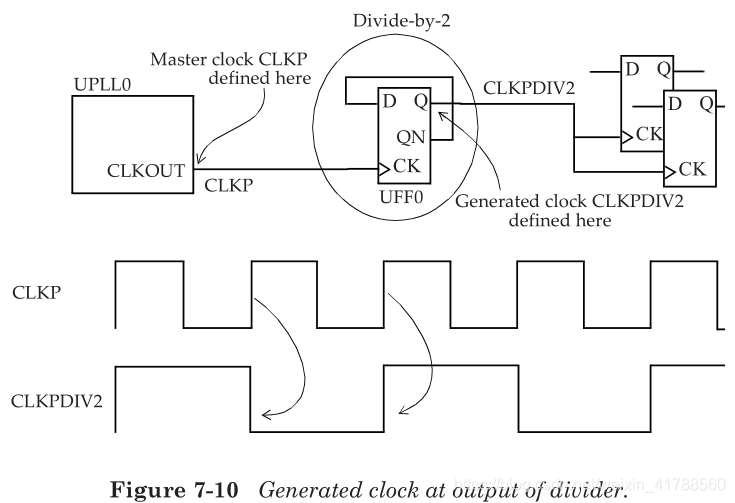

在基于主时钟的设计中生成新时钟时,可以将新时钟定义为生成时钟。例如,如果时钟有一个 3 分频电路,则可以在该电路的输出端定义一个生成时钟。这个定义是必需的,因为 STA 不知道分频逻辑输出端的时钟周期已经改变,更重要的是新的时钟周期是什么。图 7-10 显示了生成时钟的示例,该时钟是主时钟 CLKP 的 2 分频。

1 | create_clock -name CLKP 10 [get_pins UPLL0/CLKOUT] |

可以在触发器的输出端口定义一个新时钟是主时钟,而非生成时钟吗?答案是肯定的,这确实是可能的,但是它也有一些缺点。定义主时钟而不是生成时钟会创建一个新的时钟域。通常这不是问题,除了在设置STA约束时需要处理更多的时钟域外。相反,将新时钟定义为生成时钟不会创建新的时钟域,并且生成时钟会被认为与其主时钟同相,生成时钟不需要进行额外的约束。因此,尽量将内部新生成的时钟定义为生成时钟,而不是将其声明为另一个主时钟。

主时钟和生成时钟之间的另一个重要区别是时钟源的概念。在主时钟中,时钟的源点位于主时钟的定义点。在生成时钟中,时钟源是主时钟的源,而不是生成时钟的源。这意味着在时钟路径报告中,时钟路径的起点始终是主时钟定义点。这是生成时钟相对于定义新主时钟的一大优势,因为对于新主时钟的情况不会自动包含源延迟。

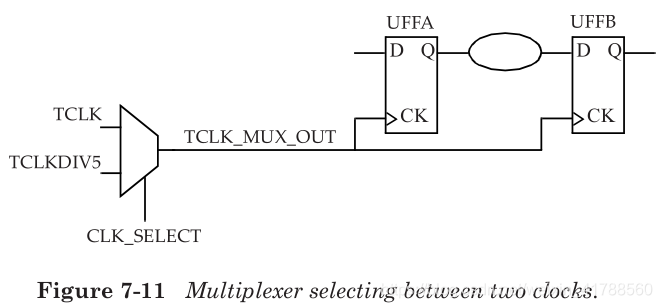

图 7-11 显示了一个多路复用器的示例,其两个输入都有时钟。在这种情况下,无需在多路复用器的输出上定义时钟。如果选择信号设置为常数,多路复用器的输出会自动获得正确的时钟传播。如果多路复用器的选择引脚不受约束,则两个时钟都通过多路复用器传播以供 STA 使用。在这种情况下,STA 可能会报告 TCLK 和 TCLKDIV5 之间的路径。请注意,这种路径是不可能的,因为选择线只能选择多路复用器输入之一。在这种情况下,可能需要设置一条错误路径或指定这两个时钟之间的独占时钟关系,以避免报告错误路径。这当然假设设计中其他地方的 TCLK 和 TCLKDIV5 之间没有路径。

如果多路复用器选择信号不是静态的并且可以在设备操作期间发生变化,会发生什么情况?在这种情况下,会对多路复用器输入端进行时钟门控(clock gating)检查。时钟门控检查在第 10 章中解释;这些检查确保多路复用器输入处的时钟相对于多路复用器选择信号安全切换。

图 7-12 显示了一个示例,其中时钟 SYS_CLK 由触发器的输出进行门控。由于触发器的输出可能不是常数,因此处理这种情况的一种方法是在和单元的输出处定义一个与输入时钟相同的生成时钟。

1 | create_clock 0.1 [get_ports SYS_CLK] |

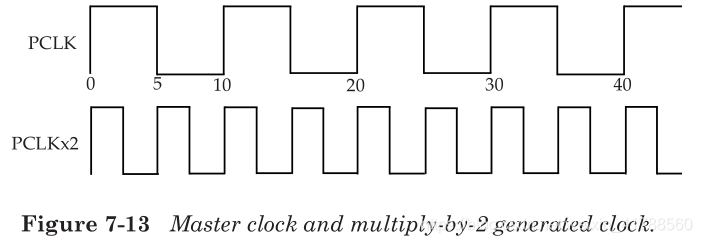

下一个示例是频率高于源时钟频率的生成时钟。图 7-13 显示了波形。

1 | create_clock -period 10 -waveform {0 5} [get_ports PCLK] |

请注意,-multiply_by 和 -divide_by 选项指的是时钟频率,即使在主时钟定义中指定了时钟周期。

时钟门控单元输出的主时钟示例(Example of Master Clock at Clock Gating Cell Output)

考虑图7-14中所示的时钟门控示例,两个时钟分别输入进一个与门单元中,问题是与门单元的输出是什么呢?如果与门单元的输入均为时钟,则可以安全地在与门单元的输出端定义一个新的主时钟,因为该单元的输出与任何一个输入时钟都没有相位关系的可能性很小。

1 | create_clock -name SYS_CLK -period 4 -waveform {0 2} \ |

在内部引脚上创建时钟的一个缺点是它会影响路径延迟计算并迫使设计人员手动计算源延迟。

使用Edge和Edge_shift选项生成时钟(Generated Clock using Edge and Edge_shift Options)

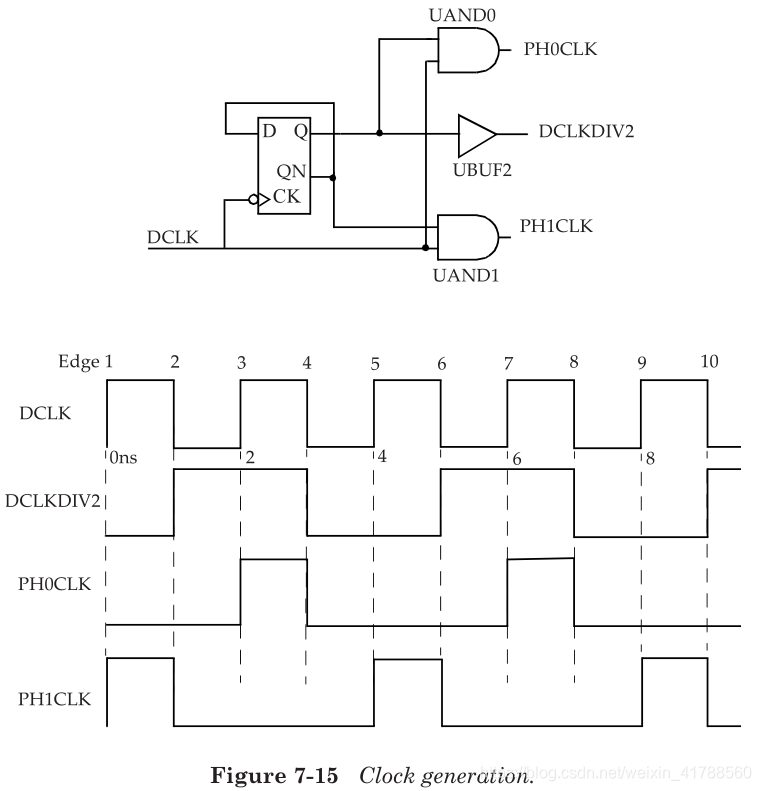

图 7-15 显示了生成时钟的示例。除了两个异相时钟之外,还会生成一个 2 分频时钟。图中还显示了时钟的波形。

下面给出了该示例中所有时钟的定义。衍生时钟的定义使用了-edges选项,这是定义衍生时钟的另一种方法。该选项采用源主时钟{上升,下降,上升}的边沿列表,以形成新的衍生时钟。主时钟的第一个上升沿是沿1,第一个下降沿是沿2,下一个上升沿是沿3,依此类推。

1 | create_clock 2 [get_ports DCLK] |

如果生成时钟的第一个边沿是下降沿怎么办?考虑生成的时钟 G3CLK,如图 7-16 所示。可以通过指定边沿 5、7 和 10 来定义此类生成的时钟,如下面的时钟约束所示。自动推断 1ns 处的下降沿。

1 | create_generated_clock -name G3CLK -edges {5 7 10} \ |

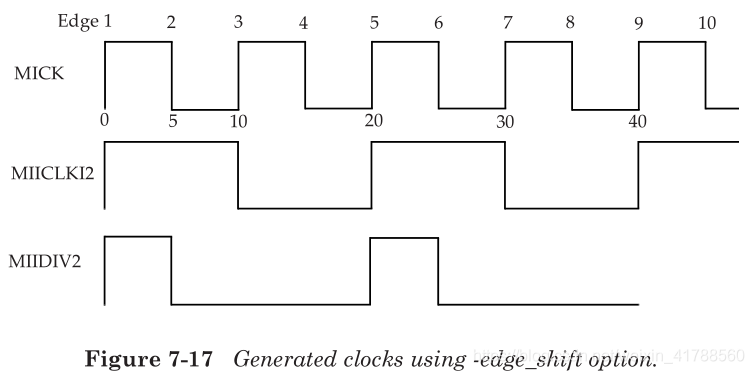

-edge_shift 选项可与 -edges 选项结合使用,以指定相应边沿的任何移位以形成新生成的波形。它指定边列表中每个边的移动量(以时间为单位)。这是使用此选项的示例。

1 | create_clock -period 10 -waveform {0 5} [get_ports MIICLK] |

边沿列表中的边沿列表必须按非递减顺序排列,但同一边沿可用于两个条目以指示独立于源时钟占空比的时钟脉冲。上例中的 -edge_shift 选项指定第一个边沿是通过将(源时钟的边沿 1)移动 0ns 获得的,第二个边沿是通过将(源时钟的边沿 1)移动 5ns 获得的,第三个边沿是通过以下方式获得的将(源时钟的边沿 5)移动 0ns。图 7-17 显示了波形。

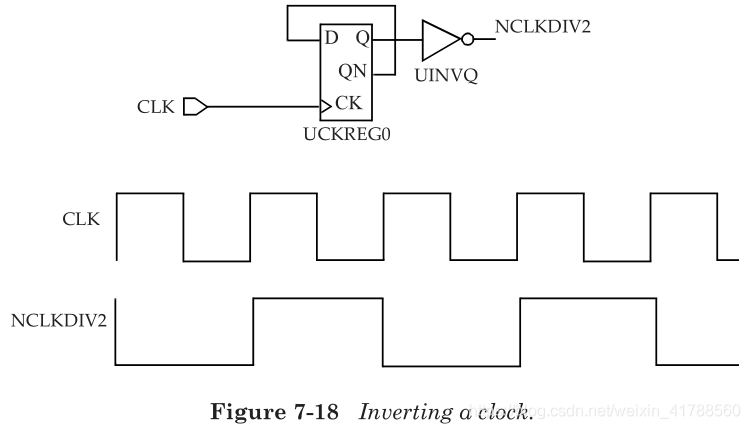

使用Invert 选项生成的时钟(Generated Clock using Invert Option)

这是生成时钟的另一个示例;这个使用 -invert 选项。

1 | create_clock -period 10 [get_ports CLK] |

-invert 选项在应用所有其他生成的时钟选项后将反转应用于生成的时钟。图 7-18 显示了生成这种反相时钟的原理图。

生成时钟的时钟延迟(Clock Latency for Generated Clocks)

也可以为生成的时钟指定时钟延迟。在生成时钟上指定的源延迟指定了从主时钟定义到生成时钟定义的延迟。因此,到由生成时钟驱动的触发器的时钟引脚的总时钟延迟是主时钟的源延迟、生成时钟的源延迟和生成时钟的网络延迟之和。如图 7-19 所示。

一个生成时钟可以有另一个生成时钟作为其源,即可以有生成时钟的生成时钟,以此类推。但是,生成的时钟只能有一个主时钟。生成时钟的更多示例将在后面的章节中描述。

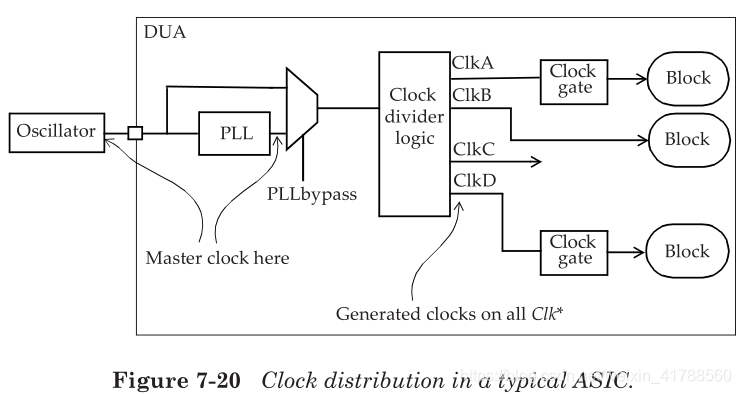

典型时钟生成场景(Typical Clock Generation Scenario)

图 7-20 显示了时钟分布如何出现在典型 ASIC 中的场景。振荡器在芯片外部并产生低频(典型值 10-50 MHz)时钟,片上 PLL 将其用作参考时钟以生成高频低抖动时钟(典型值 200-800 MHz) .然后将该 PLL 时钟馈送到时钟分频器逻辑,该逻辑为 ASIC 生成所需的时钟。

在时钟分配的一些分支上,可能有时钟门,用于在必要时关闭设计的非活动部分的时钟以节省功耗。 PLL 的输出端还可以有一个多路复用器,以便在必要时可以绕过 PLL。

在进入设计的芯片输入引脚上为参考时钟定义了一个主时钟,在 PLL 的输出端定义了第二个主时钟。 PLL 输出时钟与参考时钟没有相位关系。因此,输出时钟不应是参考时钟的生成时钟。最有可能的是,时钟分频器逻辑生成的所有时钟都被指定为 PLL 输出的主时钟的生成时钟。

约束输入路径(Constraining Input Paths)

本节将介绍输入路径的约束。这里需要注意的一点是,STA无法检查不受约束的路径上的任何时序,因此需要约束所有路径以进行时序分析。在后面的章节中会介绍一些示例,其中一些示例可能并不关心某些逻辑,因而这些输入路径可能可以不用约束。例如,设计人员可能并不在乎一些输入控制信号的时序,因此可能并不需要进行本节中将要介绍的时序检查。但是,本节假定我们要约束全部的输入路径。

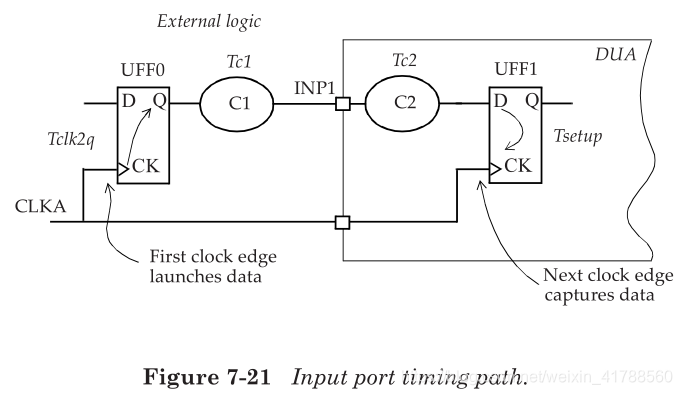

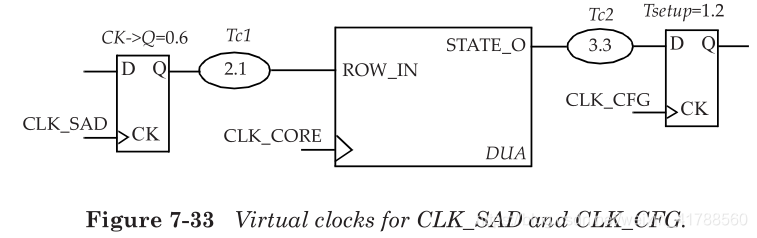

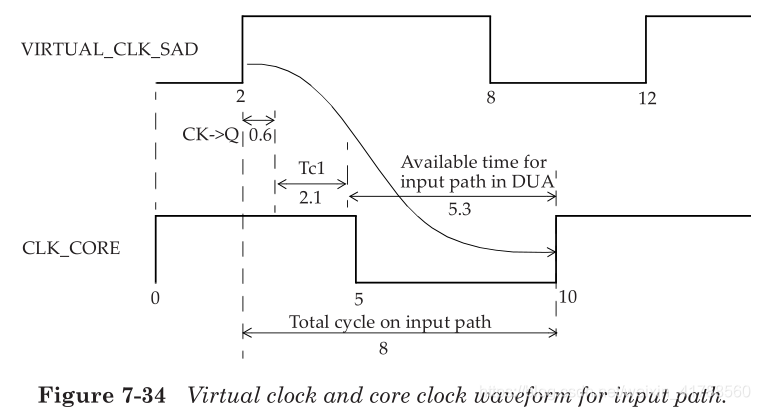

图 7-21 显示了被分析设计 (DUA) 的输入路径。触发器 UFF0 位于设计外部,并向设计内部的触发器 UFF1 提供数据。数据通过输入端口 INP1 连接。

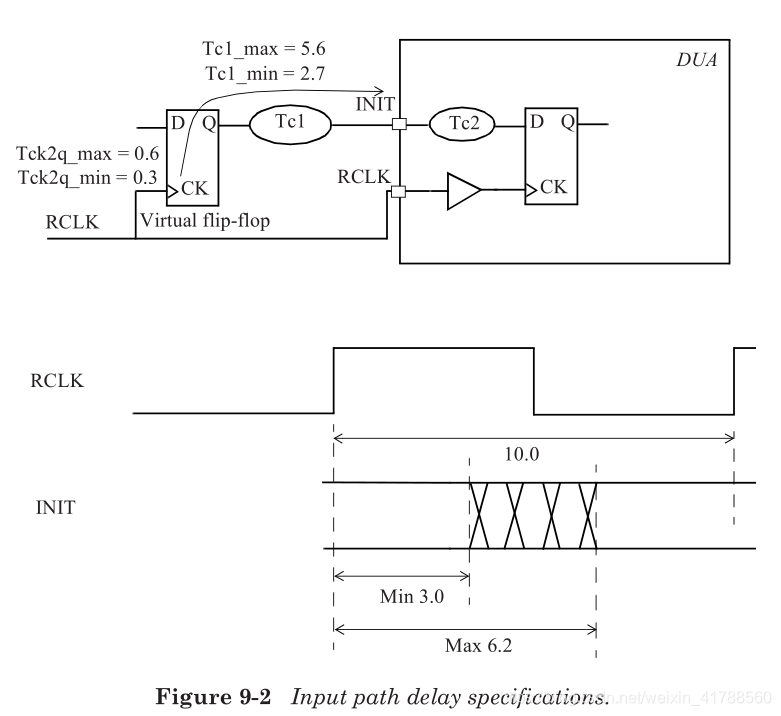

CLKA 的时钟定义指定了时钟周期,它是两个触发器 UFF0 和 UFF1 之间可用的总时间量。外部逻辑所用的时间是 Tclk2q,即启动触发器 UFF0 的 CK 到 Q 延迟,加上 Tc1,即通过外部组合逻辑的延迟。因此,输入引脚 INP1 上的延迟规范定义了 Tclk2q 加上 Tc1 的外部延迟。在本例中,此延迟是相对于时钟 CLKA 指定的。

这是输入延迟约束。

1 | set Tclk2q 0.9 |

该约束指定输入 INP1 上的外部延迟为 1.5ns,这与时钟 CLKA 相关。假设 CLKA 的时钟周期为 2ns,则 INP1 引脚的逻辑只有 500ps (= 2ns - 1.5ns) 可用于在设计内部传播。此输入延迟规范映射到输入约束,即 Tc2 加上 UFF1 的 Tsetup 必须小于 500ps,触发器 UFF1 才能可靠地捕获触发器 UFF0 启动的数据。请注意,上面的外部延迟被指定为最大数量。

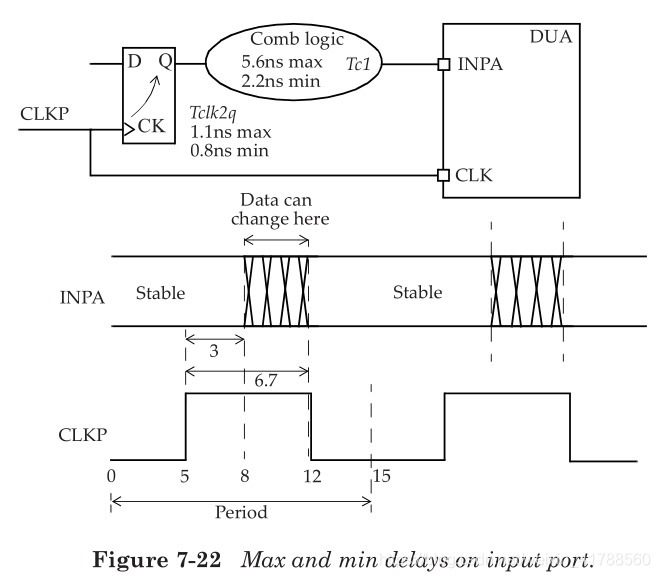

让我们考虑同时考虑最大和最小延迟的情况,如图 7-22 所示。以下是此示例的限制条件。

1 | create_clock -period 15 -waveform {5 12} [get_ports CLKP] |

INPA 的最大和最小延迟源自 CLKP 到 INPA 的延迟。最大和最小延迟分别指最长和最短路径延迟。这些通常也可能对应于最坏情况下的慢速(最大时序角)和最佳情况下的快速(最小时序角)。因此,最大延迟对应于最大拐角处的最长路径延迟,最小延迟对应于最小拐角处的最短路径延迟。在我们的示例中,1.1ns 和 0.8ns 是 Tck2q 的最大和最小延迟值。组合路径延迟 Tc1 的最大延迟为 5.6ns,最小延迟为 2.2ns。 INPA 上的波形显示了数据到达设计输入的窗口以及预期稳定的时间。从 CLKP 到 INPA 的最大延迟为 6.7ns (= 1.1ns +5.6ns)。最小延迟为 3ns (= 0.8ns+ 2.2ns)。这些延迟是根据时钟的有效边沿指定的。在给定外部输入延迟的情况下,设计内部的可用建立时间是慢角(slow corner)下的8.3ns(= 15ns-6.7ns)和快角(fast corner)下的12ns(= 15ns-3.0ns)中的最小值。因此,8.3ns是用来可靠地捕获DUA内部数据的可用时间。

以下是输入约束的更多示例。

1 | set_input_delay -clock clk_core 0.5 [get_ports bist_mode] |

由于未指定max或min选项,因此500ps这个值将同时用于最大延迟和最小延迟。此外部输入延迟是相对于时钟clk_core的上升沿指定的(如果输入延迟是相对于时钟的下降沿指定的,则必须使用-clock_fall选项)。

约束输出路径(Constraining Output Paths)

本节将借助以下三个说明性示例描述输出路径的约束。

示例 A

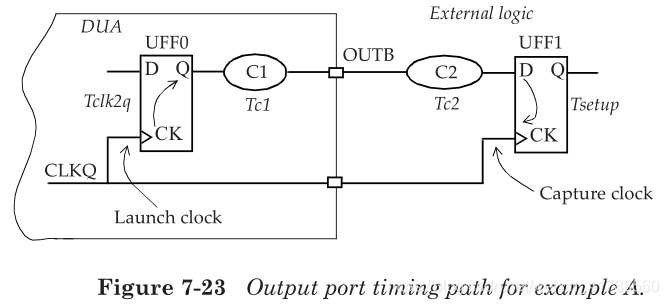

图 7-23 显示了通过分析设计的输出端口的路径示例。 Tc1 和 Tc2 是通过组合逻辑的延迟。

时钟 CLKQ 的周期定义了触发器 UFF0 和 UFF1 之间的总可用时间。外部逻辑的总延迟为 Tc2 加 Tsetup。该总延迟 Tc2 Tsetup 必须指定为输出延迟规范的一部分。请注意,输出延迟是相对于捕获时钟指定的。数据必须及时到达外部触发器UFF1以满足其建立时间要求。

1 | set Tc2 3.9 |

这指定相对于时钟边沿的最大外部延迟为 Tc2 加 Tsetup;并且应该对应5ns的延迟。可以类似地指定最小延迟。

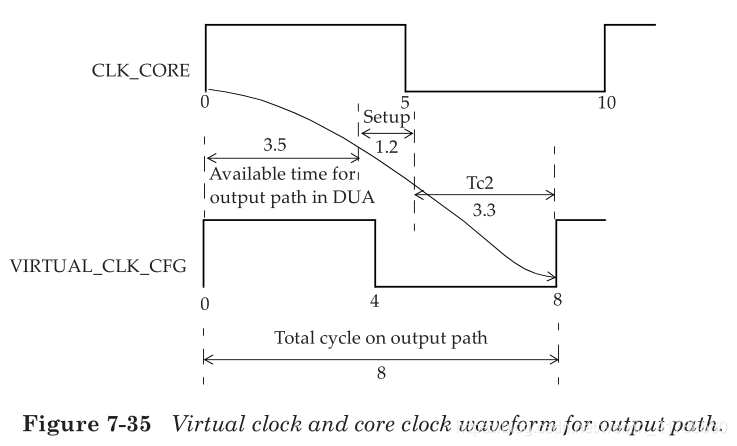

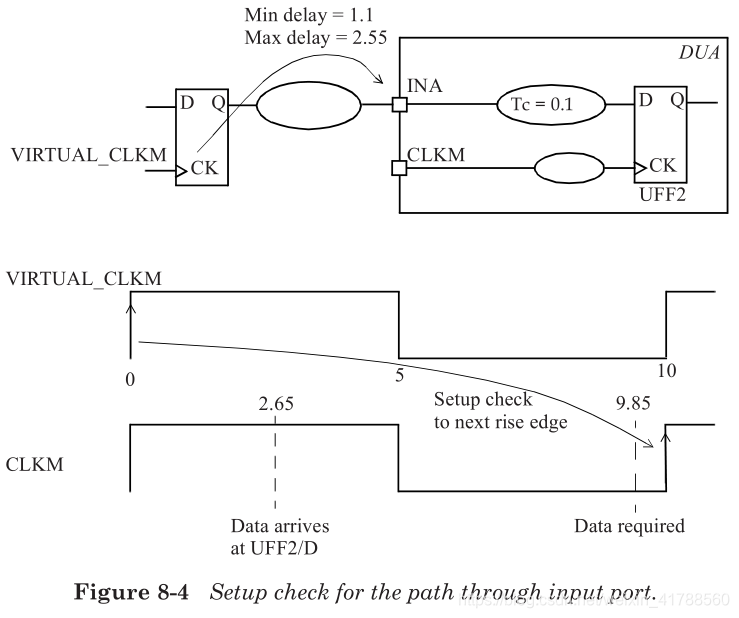

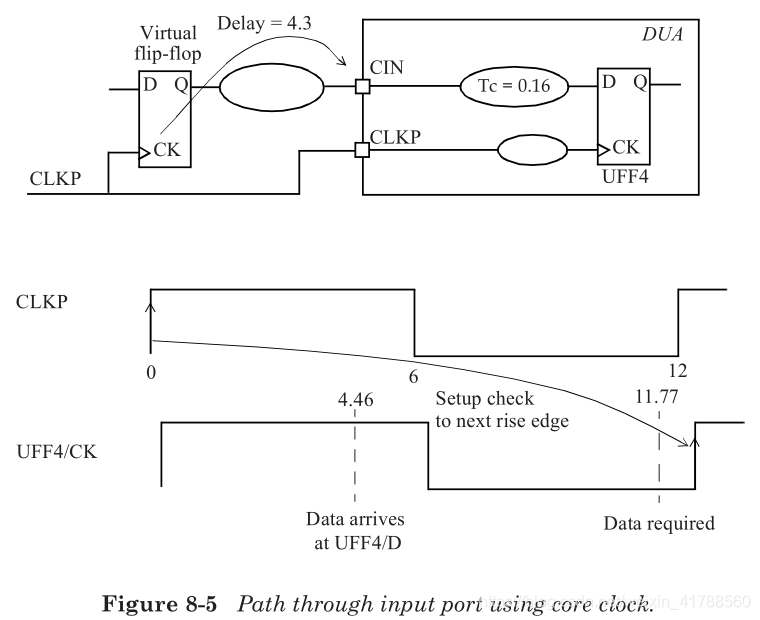

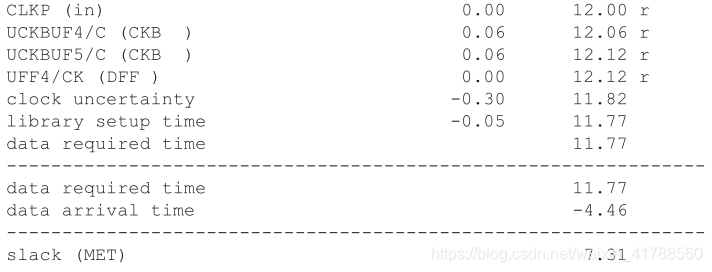

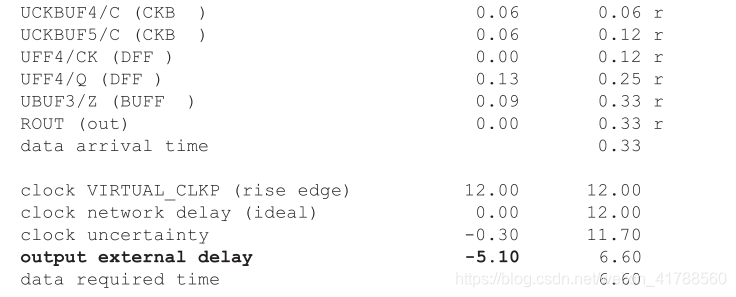

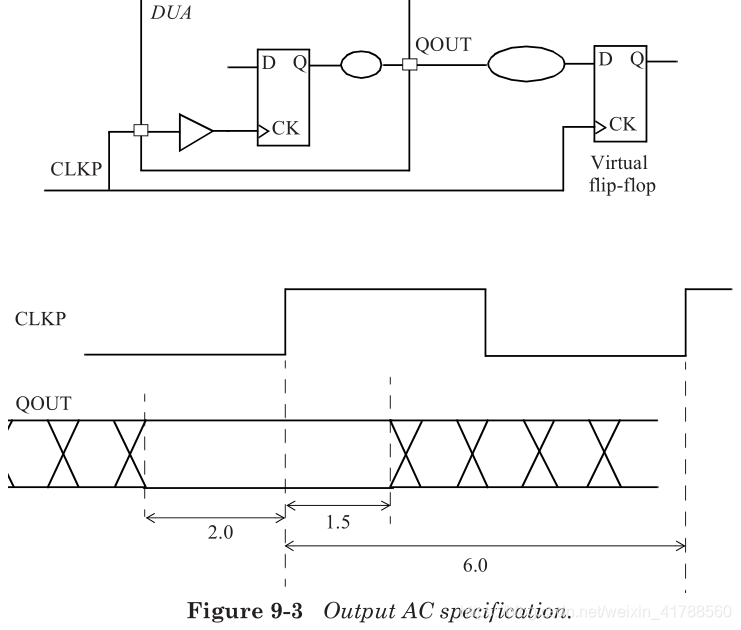

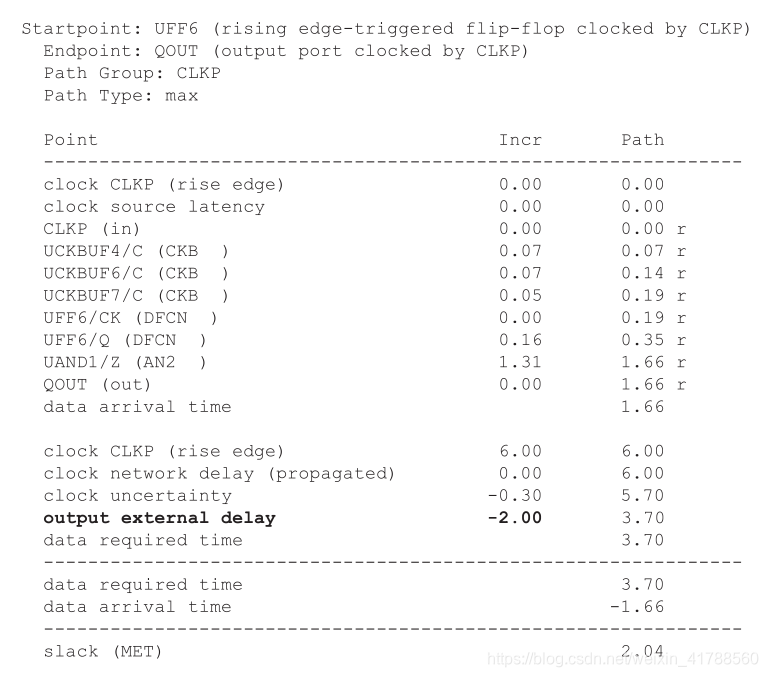

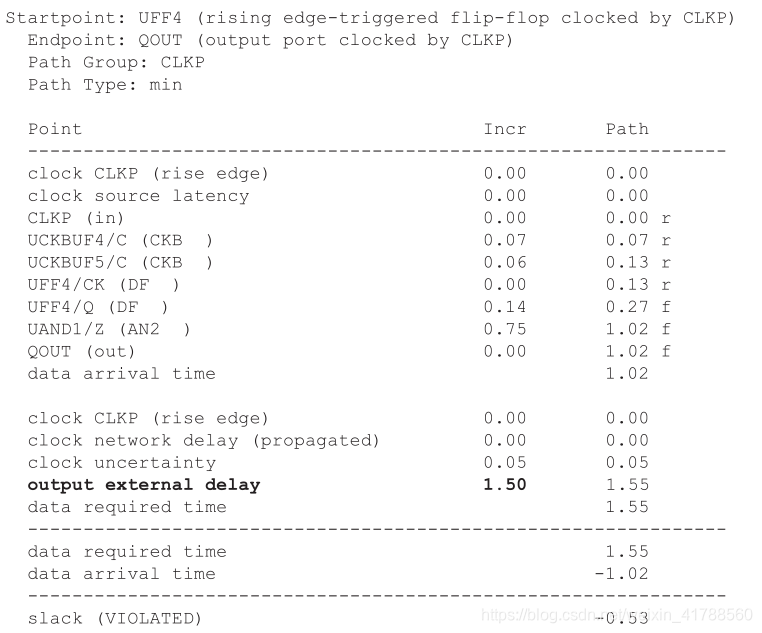

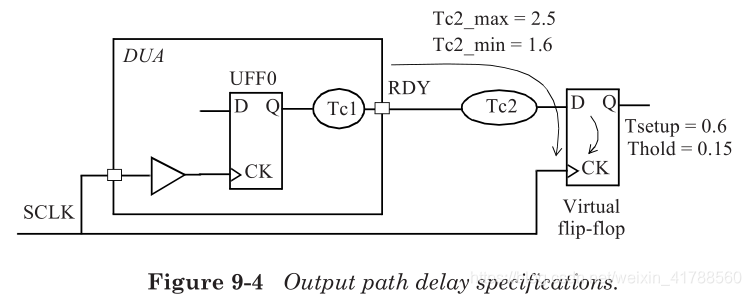

示例 B